### Mask Assignment and Synthesis of DSA-MP Hybrid Lithography for sub-7nm Contacts/Vias

Yasmine Badr, EE Department, UCLA J. Andres Torres, Mentor Graphics Puneet Gupta, EE Department, UCLA

ybadr@ucla.edu

This work was partly supported by IMPACT+ center. <u>http://impact.ee.ucla.edu</u>

## Motivation

Directed Self Assembly (DSA) is a strong candidate for future technology nodes

- BUT Pure DSA can not achieve 7nm node or beyond

- Because resolution required for GP can not be delivered by 193i lithography

- Challenges in finding BCPs which can achieve that small pitch

- Integration of DSA with Multiple Patterning (MP) is attractive for sub-7nm

- Reduce number of masks → less costly process

- Potentially more flexibility in polygon sizes

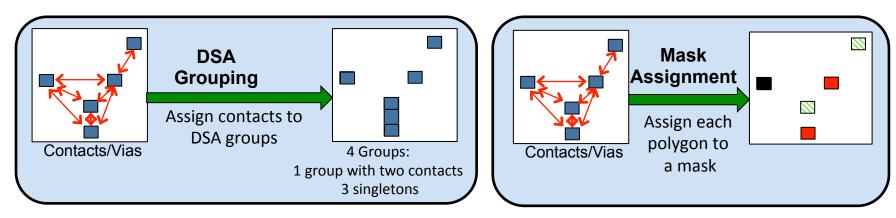

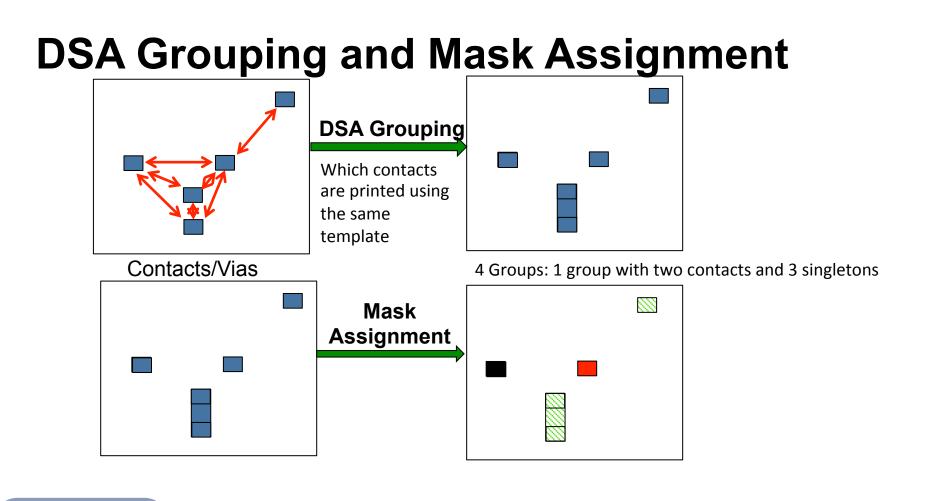

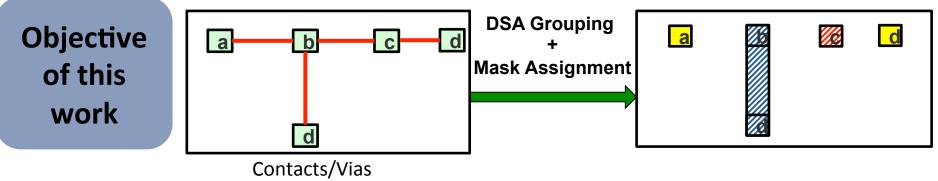

### **DSA Grouping and Mask Assignment**

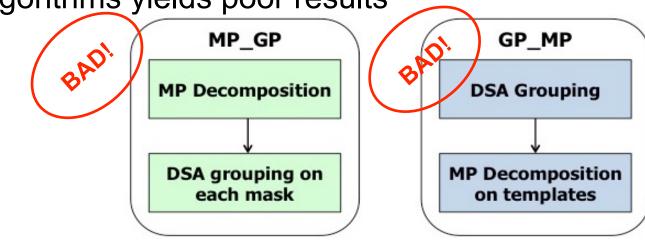

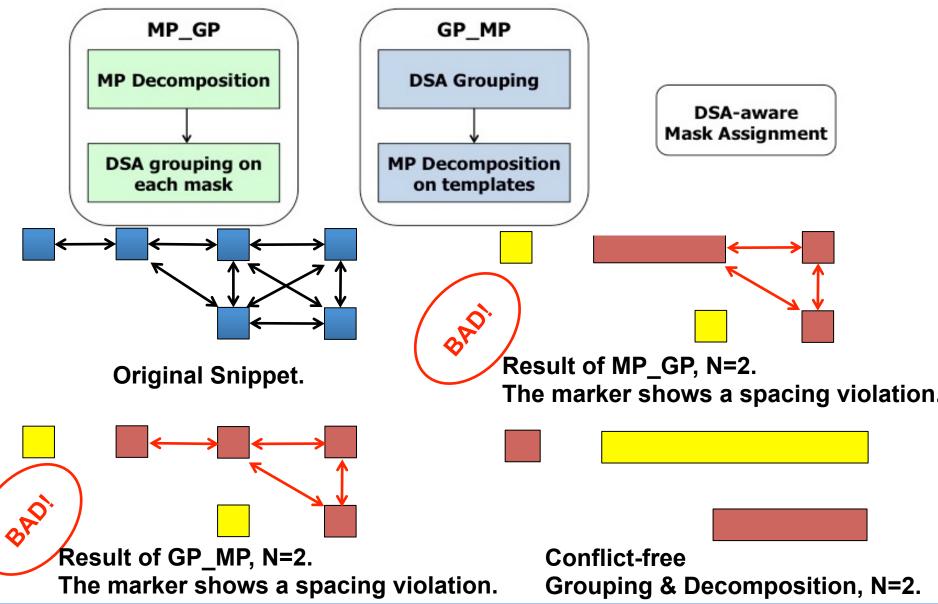

Previous work (Badr et al; SPIE'15) showed that cascading existing DSA grouping and MP decomposition algorithms yields poor results

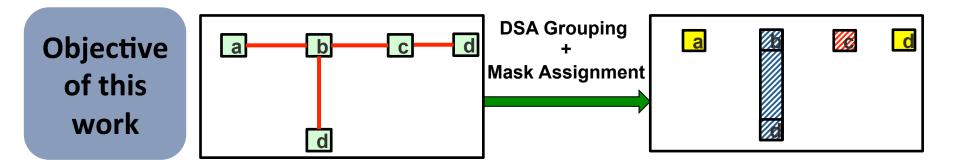

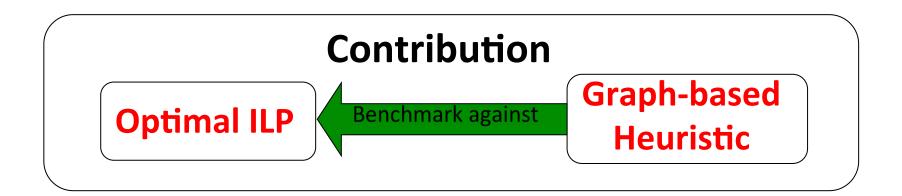

## **This Work**

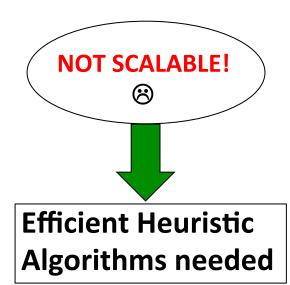

### Integer Linear Programming (ILP) Formulation

- <u>Objective</u>: minimize number of conflicts

- A conflict is when two contacts with interdistance < litho\_dist are</li>

- on same mask and

- not in same DSA group

- <u>Constraints [Simplified]</u>:

- Two "close" contacts are assigned to different masks or same DSA group if possible

- Number of contacts in each group ≤ max\_g

- ILP works for DP, TP, QP, and any number of masks that is power of two.

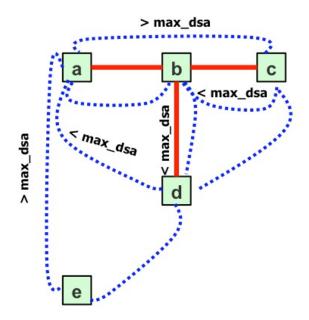

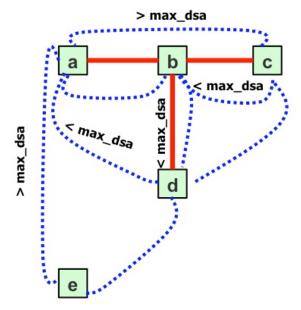

## **Hybrid Graph Representation**

- Spacing Edge: between every pair of contacts within *litho\_dist*

- 2. Grouping Edge: between every pair of neighboring contacts that can be DSA-grouped

- *min\_dsa* ≤ distance ≤ *max\_dsa*

- Collinear, on same y or x axis

- To have 193i-manufacturable templates

Blue: Spacing Edge Red: Grouping Edge

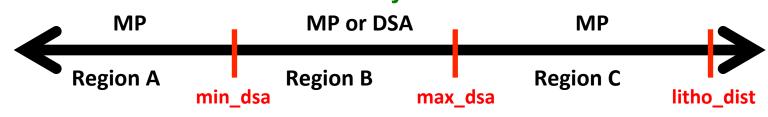

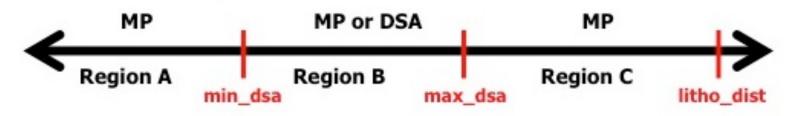

### Ranges of Distance between two polygons where spacing violation can be resolved by MP or DSA

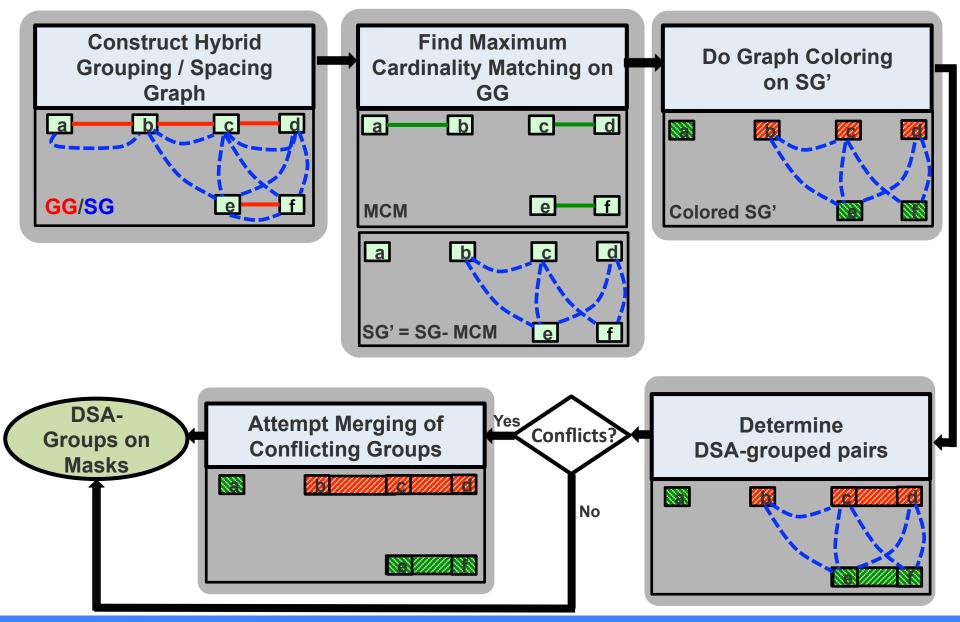

## **Proposed Heuristic**

- Maximize chance of DSA grouping → maximize possibility of eliminating conflicts

- Find max number of grouping edges with no common nodes

Blue: Spacing Edge Red: Grouping Edge

### **Proposed Heuristic Algorithm: MCM\_H**

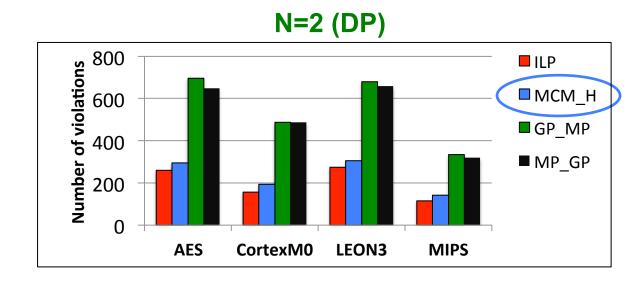

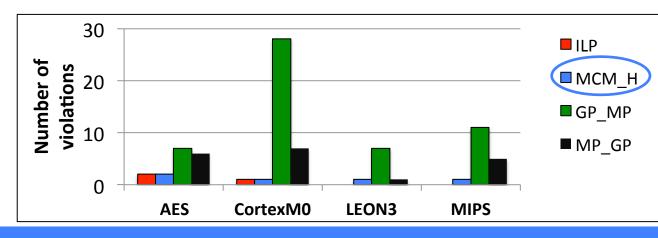

### Results

N=3 (TP)

| Test case | Number of Vias |

|-----------|----------------|

| AES       | 48123          |

| CortexM0  | 35255          |

| LEON3     | 93474          |

| MIPS      | 34784          |

MCM\_H is ~200x faster than ILP. (Max runtime on our test cases is 13s.)

MCM\_H has 16.3% more violations than ILP.

MCM\_H has 56% fewer violations than sequential approaches (GP\_MP & MP\_GP)

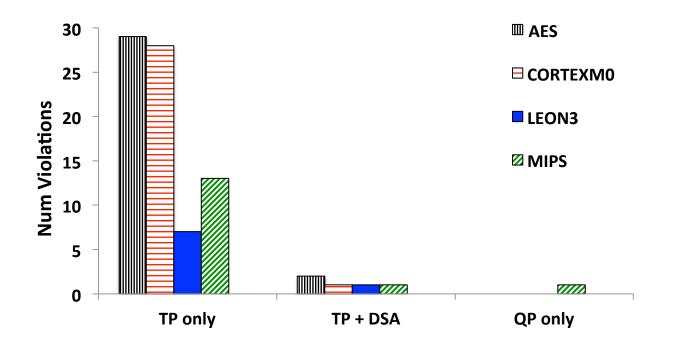

### Can we really reduce one mask?

#### Number of violations with TP only, TP+DSA using MCM\_H and QP only

## Conclusion

- We proposed optimal ILP formulation to solve the simultaneous DSA grouping + MP decomposition problem for a hybrid DSA-MP process.

- We presented an efficient graph-based heuristic (MCM\_H).

- MCM\_H produces 16.3% more violations than ILP, but is ~200x faster.

- MCM\_H produce 56% fewer violations than naïve sequential approaches which cascade grouping and decomposition.

## **Future Work**

- Explore different MP+DSA integration schemes.

- Allow more flexible grouping enabled by EUV or more restricted due to Sidewall image transfer e.g. SAQP.

## **THANK YOU!**

ybadr@ucla.edu

# BACKUP

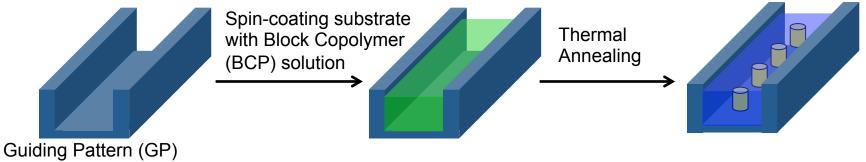

## **Hybrid DSA-MP Process**

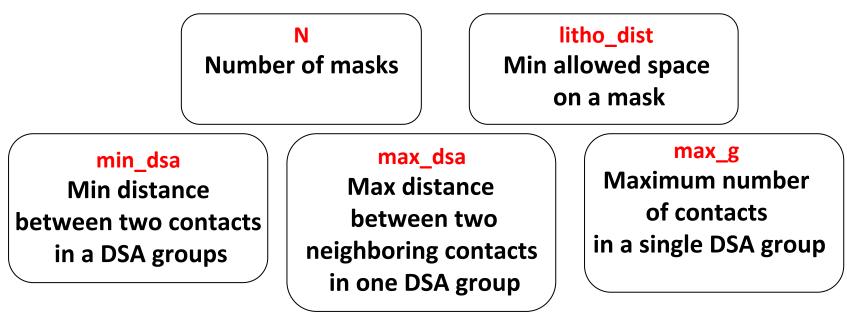

#### **Important Parameters and Rules**

Ranges of Distance between two polygons where spacing violation can be resolved by MP or DSA

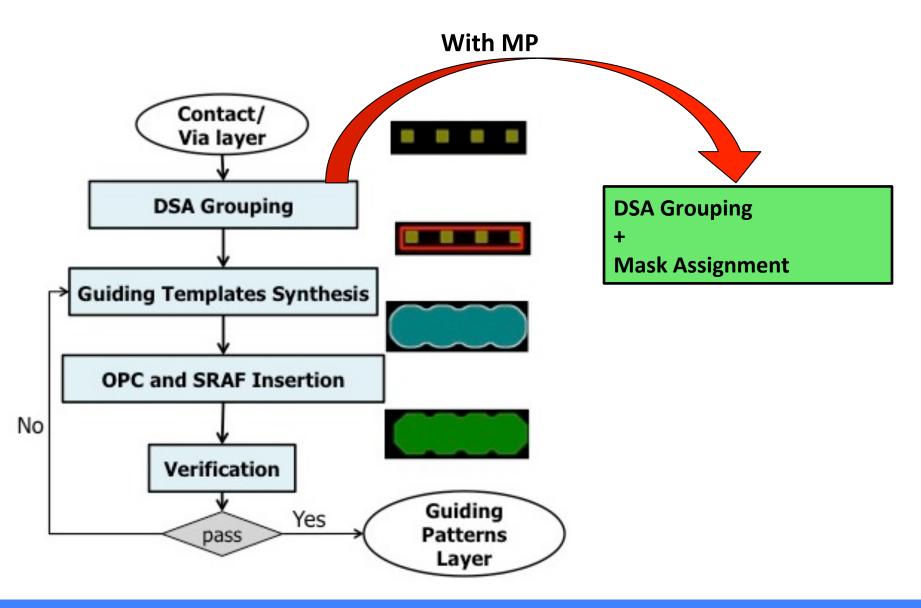

### **CAD flow for DSA**

### **Alternative Flows**

### **Experiments and Results**

- Test cases have been synthesized, placed and routed using commercial 45nm SOI libraries, then scaled and sized

- Used via1 layer. After scaling: min space=21nm, via width=14nm

- Implemented in C++, using Boost library, OpenAccess

- Used Calibre Multi-patterning tool

Number of vias in test cases

Parameters u

| Test case | Number of Vias |

|-----------|----------------|

| AES       | 48123          |

| CortexM0  | 35255          |

| LEON3     | 93474          |

| MIPS      | 34784          |

| min_dsa       | 20               |

|---------------|------------------|

| max_dsa       | 42               |

| litho_dist    | 66               |

| max_g         | 2                |

| contact width | 14               |

| $L_0$         | 34               |

| N             | 2 (DP) and 3(TP) |