## Impact of Range and Precision on Standard Cell Libraries

John Lee Puneet Gupta UCLA Electrical Engineering {lee@ee.ucla.edu, puneet@ee.ucla.edu}

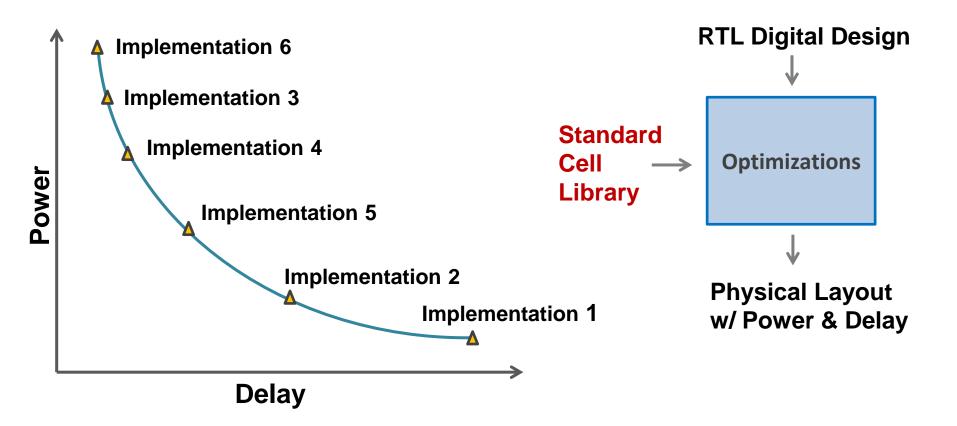

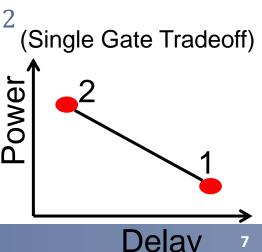

## Introduction: Tradeoff Between Power and Delay

## Motivation: Power and Delay Tradeoffs

## Motivation: FinFET Standard Cell Libraries

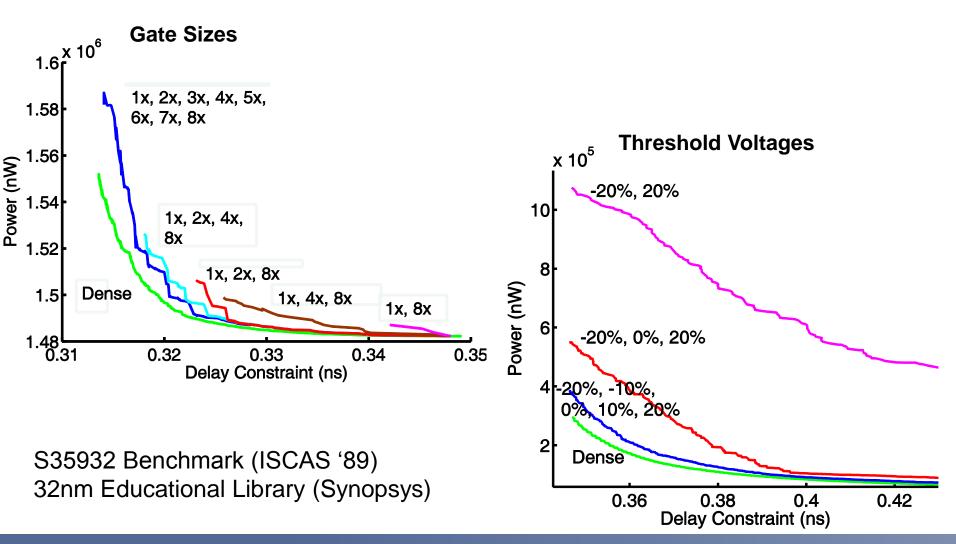

- Gate sizes quantized (1x, 2x, 3x, 4x, ...)

- Affects the delay range and feasibility

- Limited availability of Threshold Voltages

- Created by adjusting gate workfunction or use the back-gate

- Number of threshold voltages will likely be limited [Warnock 11]

- What does this mean for resulting designs? How can this impact be quantified?

## Outline

- 1. Prior Approaches to finding the impact of the standard cell library

- 2. Expressions to estimate suboptimality

- Gate Sizes

- Threshold Voltages

- 3. Experimental validation

- Gate sizes

- Threshold voltages

- 4. Discussion on Range and Precision

# **Prior Approaches**

- Experiments and heuristics for selecting library sizes

- Using Quantization Error + Experimental Results [Beeftink et al 98, 00]

$so_{Q(SiZe)} = min_{s_i}|s_i - s|$

- Experimental Results to determine best library sizes

- Use the geometric progression 1.3x,  $(1.3)^2x$ ,  $(1.3)^3x$ ,  $(1.3)^4x$ , etc.

- [Singhal and Girishankar 06]

- Use .5x, 1x, 2x, 3x, 4x, 5x

- [Afonso et al 09]

- Prior art could not predict suboptimality of size selection

- More difficult and stronger question

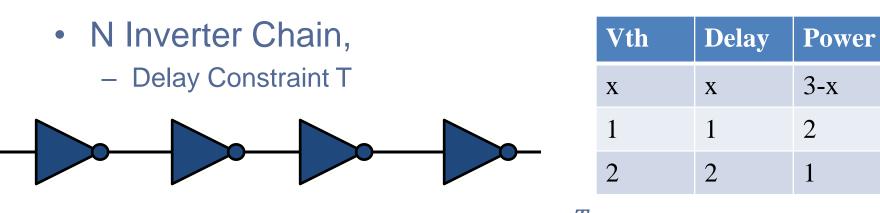

# **Thought Experiment #1**

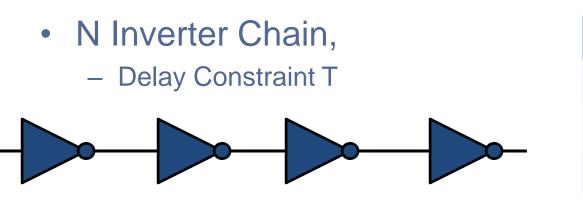

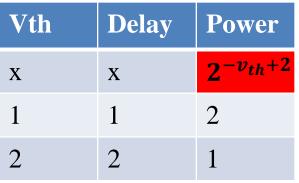

- Continuous Optimum for  $v_{th} = \frac{T}{N}$

- With  $v_{th} \in \{1, 2\}$

- Discrete Optimum: have [T N] gates at  $v_{th} = 2$

- Suboptimality is at most 1

- Proportional to 1/N & decreases as  $N \to \infty$

# **Thought Experiment #2**

- Same Continuous Optimum:  $v_{th} = \frac{T}{N}$

- With  $v_{th} \in \{1, 2\}$

- Discrete Optimum: have [T N] gates at  $v_{th} = 2$

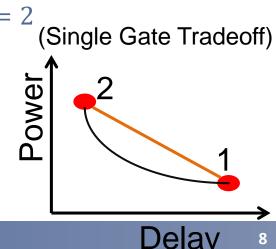

- Suboptimality does not decrease as  $N \rightarrow \infty$

# **Suboptimality and Convexity**

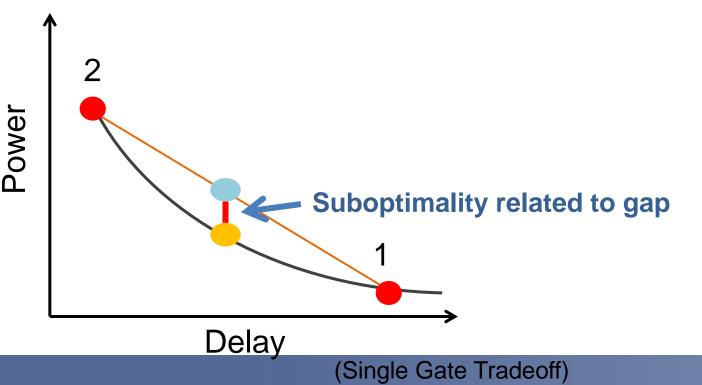

- Power vs. Delay Tradeoff curves are convex nonincreasing functions

- Convex curves have the property that any secant line lies at or above the curve

## Suboptimality expressions: vt

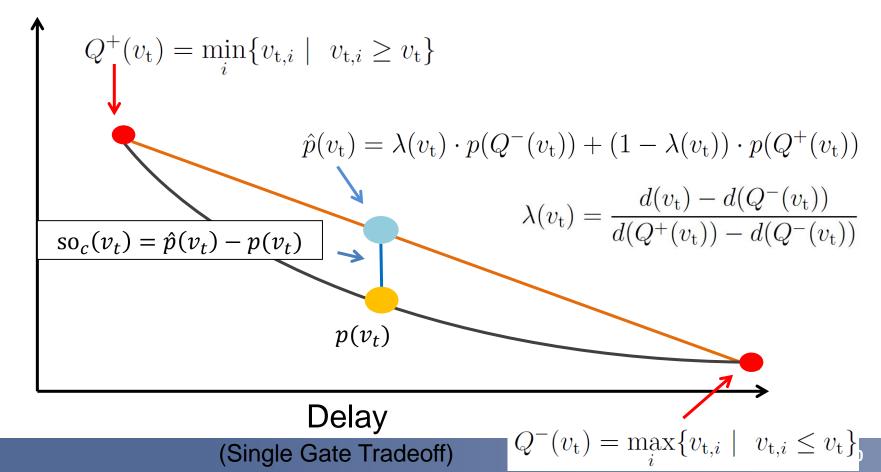

• Suboptimality is the difference between the upper line and the lower tradeoff curve

Power

# **Suboptimality of Full Design**

• Sum of individual gate suboptimalities

$$so_c(Design) = \sum_{\{\forall g \in Design\}} so_c(v_t)$$

with

$so_c(v_t) = \hat{p}(v_t) - p(v_t)$ : Per gate suboptimality  $\hat{p}(v_t)$ : Achievable power tradeoff with given sizes  $p(v_t)$ : Continuous optimal size  $(v_t)$  and power  $p(v_t)$

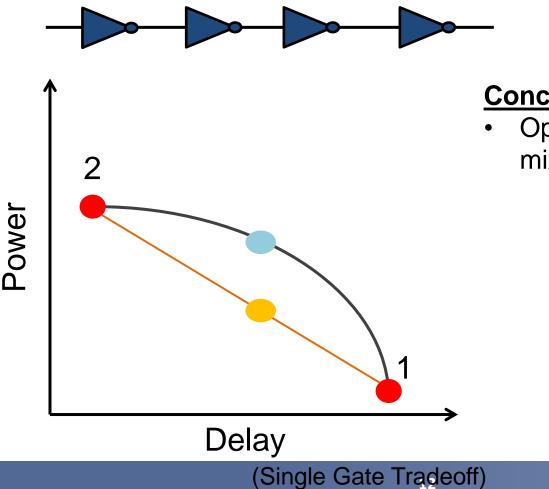

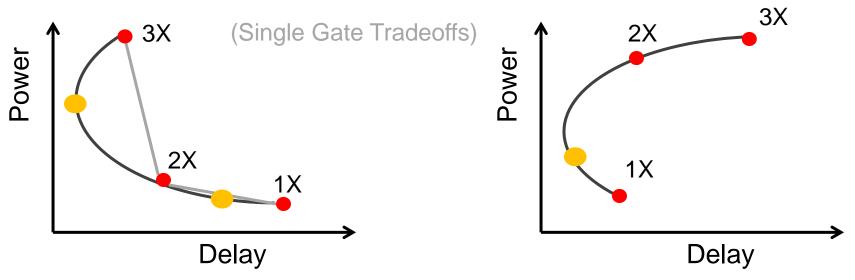

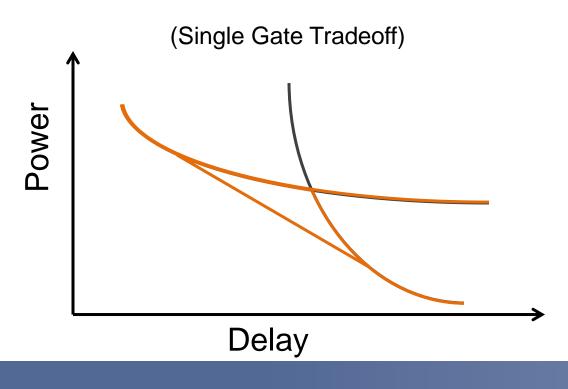

## **Non-convex Power Delay Curves**

#### Non-convex curves

#### **Concave Curves**

Optimal Solution Utilizes a mixture of (1) and (2)

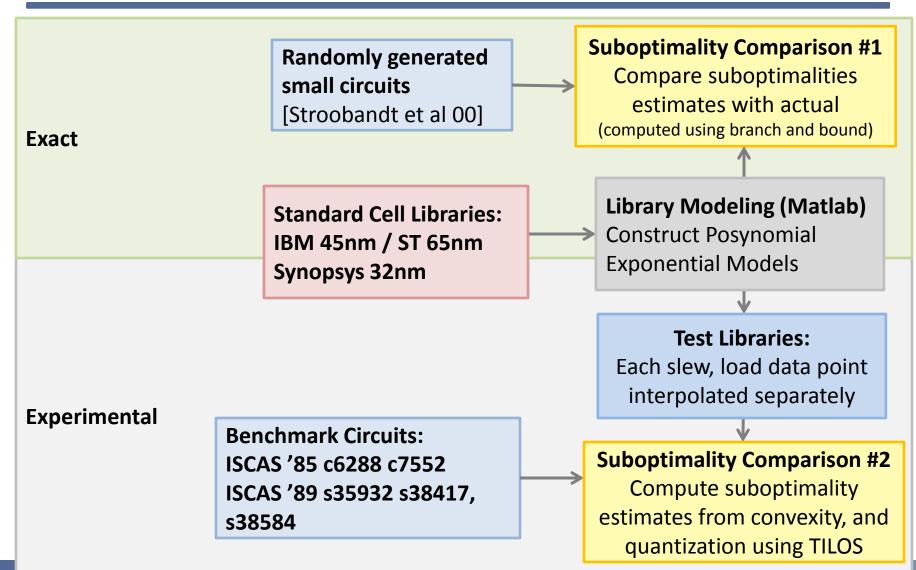

# Experimental Setup: vt assignment

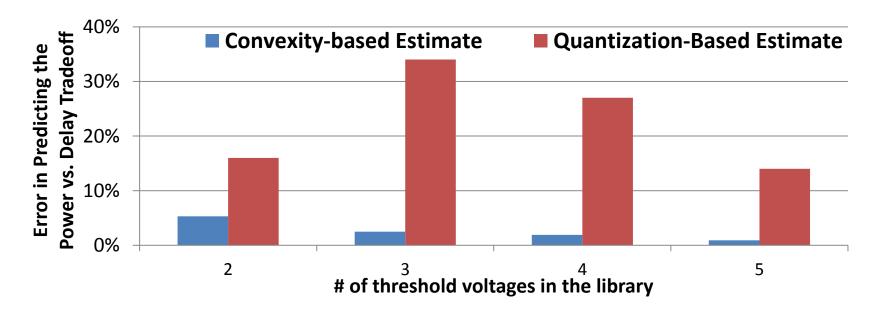

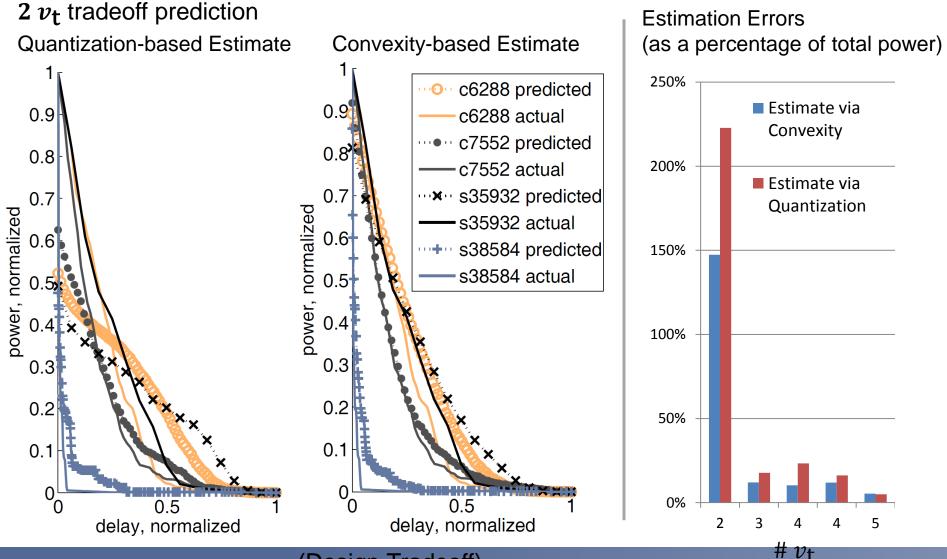

## **Experiment (Exact Methods):** Estimating the tradeoff of $v_t$ assignment

- 30 randomly generated circuits, each with size 30 using [Stroobandt 00]

- Used to predict power delay tradeoff for different  $v_t$  libraries

### **Experiment (TILOS):** Estimating the tradeoff of $v_t$ assignment

(Design Tradeoff)

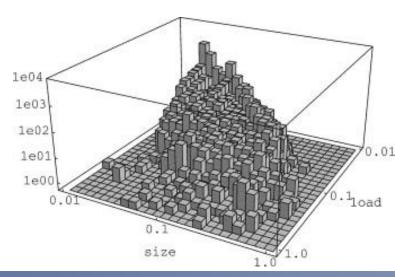

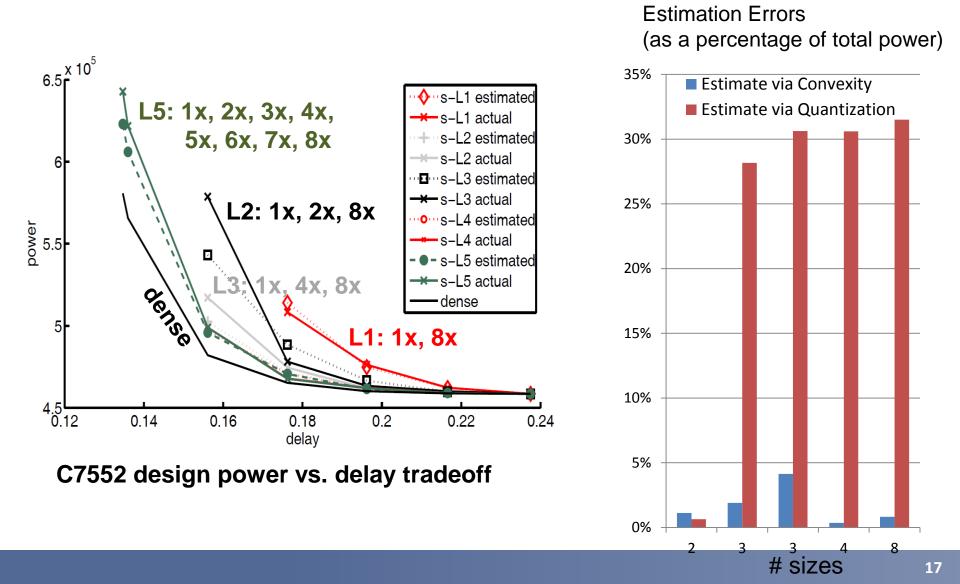

# **Extension to Gate Sizing**

- Power delay curves different for gate sizing

- Account for both delay at the input and output of the gate

- Two cases:

- Required delay is **possible** (use the same method as before)

- Required delay is **impossible** (estimate with **round-up** penalty)

- Fitting term needed (benchmark dependent)

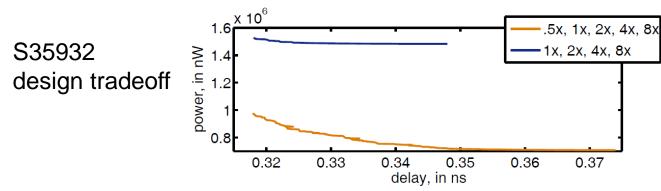

# Experiment: estimating the tradeoff of gate sizing

## Discussion: Dynamic Range Considerations

- Always need a low power option

- Dictated by the technology and allowable slew rates

- Estimate as fraction of minimum-sized devices with pos. slack

- Largest Size

- Related to the capacitive loads in a design

- Convex p/d curve tradeoff between power vs. delay is worse

- Lowest Vt

- Related to delay range needs

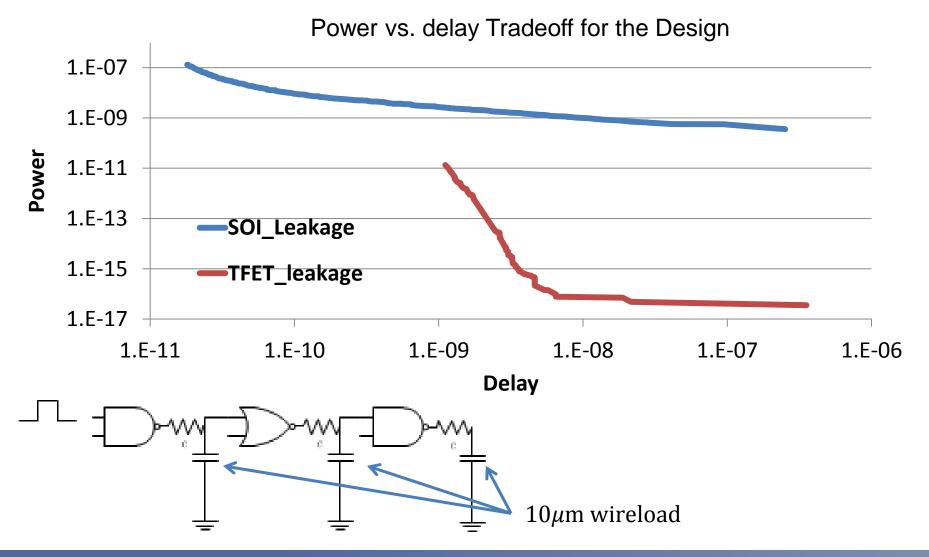

## Discussion: SOI and TFET Technology Example

(Data and plot courtesy of Shaodi Wang)

## Discussion: Mixing Technologies

- Allows for several tradeoffs:

- Use one technology

- Use both technologies but optimize independently

- Use both technologies and optimize jointly

# Summary

- Method to estimate the suboptimality related to a selection of sizes or  $v_{\rm f}$

- Related to the convexity of the power delay tradeoff

- Experimental results show strong explanatory power compared to prior work

- 2x better (gate sizing) and 10x better (threshold voltage)

- Use in determining which standard library cells to provide

- Can be used to understand impact of future technologies

- FinFet Libraries with limited size and vth availability

- Designs with mixtures of different technologies

## References

- R. Afonso, M. Rahman, H. Tennakoon, and C. Sechen. "Power efficient standard cell library design." In *IEEE Dallas Circuits and Systems Workshop, (DCAS)*, pp. 1–4, 2009.

- F. Beeftink, P. Kudva, D. Kung, and L. Stok. "Gate-size selection for standard cell libraries." *In Proc. Int. Conf. Computer-Aided Design*, pp. 545–550, Nov 1998.

- F. Beeftink, P. Kudva, D.S. Kung, R. Puri, and L. Stok. "Combinatorial cell design for CMOS libraries." *Integration, the VLSI Journal*, 29(1):67–93, 2000.

- JP Fishburn and AE Dunlop. "TILOS: A Posynomial Approach to Transistor Sizing." *In Proc. Int. Conf. Computer-Aided Design*, 1985.

- V. Singhal and G. Girishankar. "Optimal Gate Size Selection for Standard Cells in a Library." In IEEE Workshop on Design, Applications, Integration and Software, pp. 47–50, 2006.

- D. Stroobandt, P. Verplaetse, and J. van Campenhout. "Generating synthetic benchmark circuits for evaluating CAD tools," IEEE Trans. on Computer-Aided Design, 19(9):1011 –1022, sep 2000.

- T. Taghavi, C. Alpert, A. Huber, Z. Li, G. Nam, S. Ramji, "New placement prediction and mitigation techniques for local routing congestion," In Proc. Int. Conf. On Computer-Aided Design, Nov. 2010