## Incremental Gate Sizing for Late Process Changes

John Lee and Puneet Gupta lee@ee.ucla.edu, puneet@ee.ucla.edu Electrical Engineering Department UCLA

### Outline

- 1. Process change

- 2. ECO Costs

- 3. ECO Aware Design via LPECO

- 4. Experiments

- 5. Summary

### Manufacturing process

- The foundry provides designers with a model of the manufacturing process

- Information about the way transistors and interconnect

- BSIM / PTM models, Liberty (.lib) model

- Model contains information about:

- Electrical parameters: threshold voltage, saturation current, leakage current, I-V characteristics, interconnect resistance, capacitance, dielectric information

- Geometrical parameters: gate length, gate width, source / gate

/ drain capacitance

## **Manufacuring Process Changes**

# Aggressive schedules = uncertainty From ITRS 2008:

| Table DESN9 Design for Manufacturability Technol                              | ogy Require | ements      |              |              |              |              |

|-------------------------------------------------------------------------------|-------------|-------------|--------------|--------------|--------------|--------------|

|                                                                               |             |             |              |              |              |              |

| Year of Production                                                            | 2007        | 2008        | 2009         | 2010         | 2011         | 2012         |

| Normalized mask cost from public and IDM data                                 | 1           | 1.3         | 1.7          | 2.3          | 3            | 3.9          |

| % V <sub>dd</sub> variability: % variability seen in on-chip circuits         | 10%         | 10%         | <b>10</b> %  | 1 <b>0</b> % | 10%          | 10%          |

| % V <sub>th</sub> variability: doping variability impact on V <sub>th</sub> , |             |             |              |              |              |              |

| (minimum size devices, memory)                                                | 31%         | 35%         | 40%          | 40%          | 40%          | 58%          |

| % V <sub>th</sub> variability: includes all sources                           | 33%         | 37%         | <b>42</b> %  | <b>42</b> %  | <b>42</b> %  | <b>58%</b>   |

| % V <sub>th</sub> variability: typical size logic devices, all sources        | 16%         | 18%         | 20%          | 20%          | 20%          | <b>26%</b>   |

| % CD variability                                                              | 12%         | <b>12</b> % | 1 <b>2</b> % | <b>12</b> %  | 1 <b>2</b> % | 1 <b>2</b> % |

| % circuit performance variability                                             |             |             |              |              |              |              |

| circuit comprising gates and wires                                            | 46%         | 48%         | <b>49%</b>   | 51%          | 60%          | <b>63%</b>   |

| % circuit total power variability                                             |             |             |              |              |              |              |

| circuit comprising gates and wires                                            | 56%         | 57%         | 63%          | 68%          | 72%          | 76%          |

| % circuit leakage power variability                                           |             |             |              |              |              |              |

| circuit comprising gates and wires                                            | 124%        | 143%        | 186%         | 229%         | 255%         | <b>281%</b>  |

### **Solutions known, under development**

### **Solutions not known**

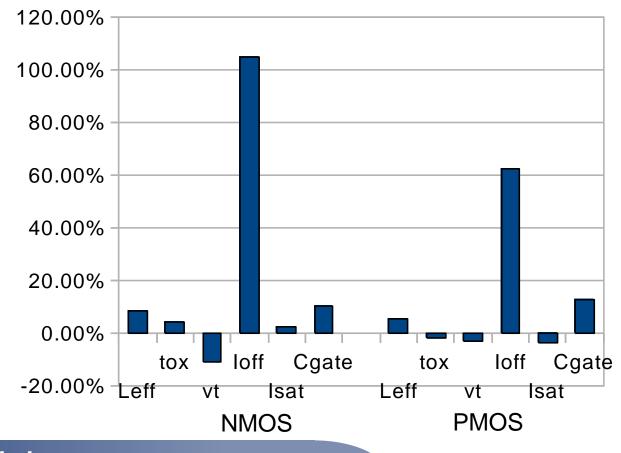

### 45nm Manufacturing Process change Example

- From April 2008 to March 2010

- Real data from a commercial 45nm process

## **Engineering Change Order (ECO)**

Design changes that are made late in the design process are referred to as an Engineering Change Order (ECO)

#### Example:

HotFab Foundry provides Design Tech Inc. with an updated set of manufacturing parameters that decrease  $I_{sat}$  (the saturation current), causing their current designs to violate timing.

They fix their design using an ECO which includes changing the gate sizes (e.g. INV X1 -> INV X8), and routing changes

### ECO = design / tool time + delays! (€€€ / \$\$\$ !) ECOs should minimize implementation costs!

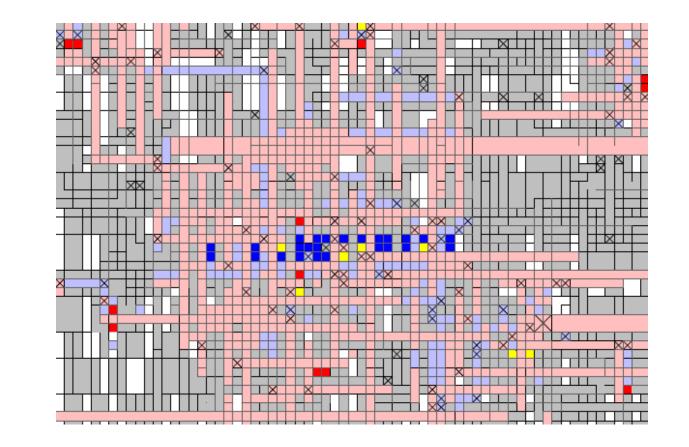

### What does an ECO cost?

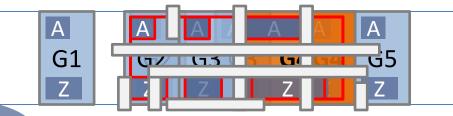

Legend

Added nets

**Deleted nets**

Moved cells

**Resized cells**

### Quantify ECO cost $\rightarrow$ Guide Optimization

### **Proposed Measures for ECO Cost**

- ECO Area Cost: Changed area

- Amount of area that must be reanalyzed for

- Parasitic Extraction & LVS / DRC

- Potential layout errors to be corrected

- ECO Timing Cost: Changed timing

- The effect of the ECO on the timing signal (circuit topology):

- # of pins with unnecessary timing changes

- The pin was not violating timing before the ECO

- Changes cause slew, crosstalk violations, in paths that run through the ECO

- Potential timing errors to be corrected

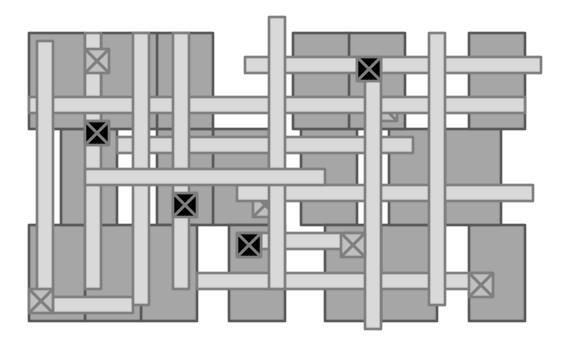

### **ECO Area Cost**

- Measured as the amount of area, in µm<sup>2</sup> that has changed

- Includes gate area, metal wires and vias

## **Estimating ECO Area Cost**

- Performing trial ECOs are too costly:

- Impractical to try all possible ECO moves

- Estimates of routing cost are needed to guide optimization

- Area Cost Estimated as a linear function of:

- Number of changed pins

- Number dislocated pins

- Old and new locations do not overlap

- Area of the pin bounding box

- Congestion over the pin bounding box

### **Estimating ECO Area Cost**

### Area Cost Estimate:

- $m_1$ : Number of affected pins

- *m*<sub>2</sub>: Number of dislocated pins *(old locations and new* locations do not overlap)

- $m_3$ : Pin bounding box area

- *m*<sub>4</sub>: Utilized area over pin bounding box (routing over all layers)

$$\hat{c}_{\text{area}} = \sum_{i=1}^{4} a_i m_i + b$$

$$a_1 = 0.0367 \ \mu m^2/\text{pin}$$

$a_2 = 0.186 \ \mu m^2/\text{pin}$

$a_3 = 5.35$

$a_4 = 9.65$

$b = .264 \ \mu m^2$

## **ECO Timing Cost**

- Timing is affected downstream and upstream

- ECO Timing cost is defined as:

- # of non-critical pins that are upstream and downstream from an ECO

### **ECO Cost Example:**

<u>Timing cost:</u> 118.9 µm<sup>2</sup>

Pin Cost: 2838 pins

### **ECO Cost Example:**

<u>Timing cost:</u> 586.6 µm<sup>2</sup>

Pin Cost: 10198 pins

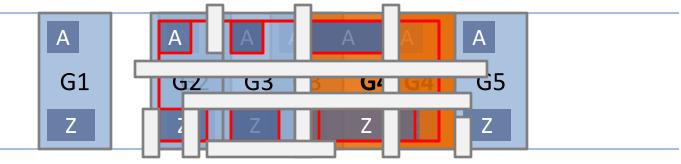

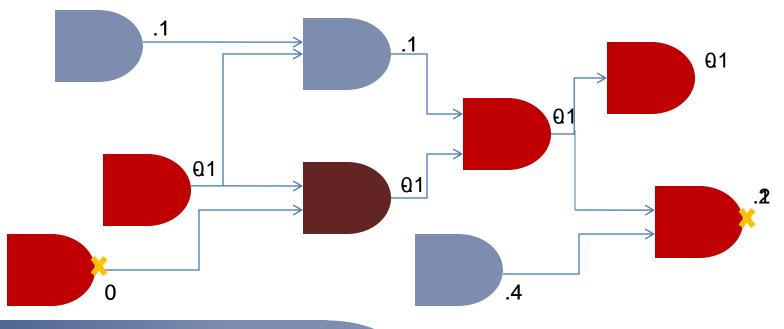

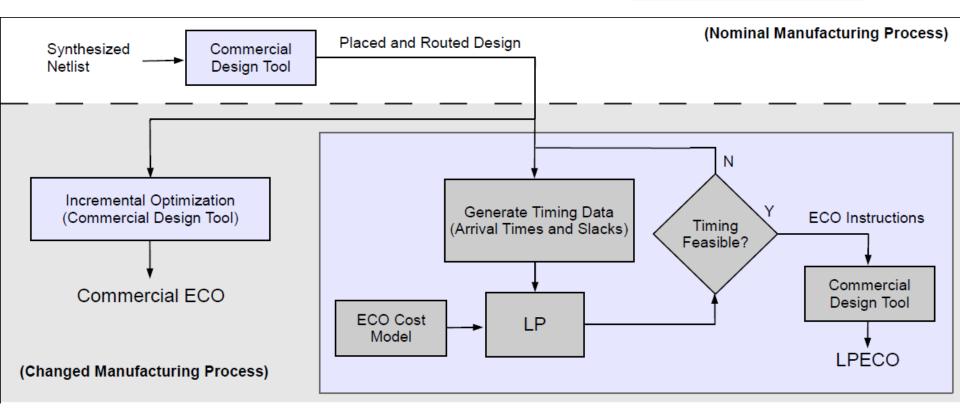

### **ECO-cost aware design via LPECO**

- Linear programming based ECO gate sizing

- Objective: ECO cost + Power cost

- Constraints: Delay (timing closure)

- Timing, power and ECO are modeled as a function of the candidate gate size

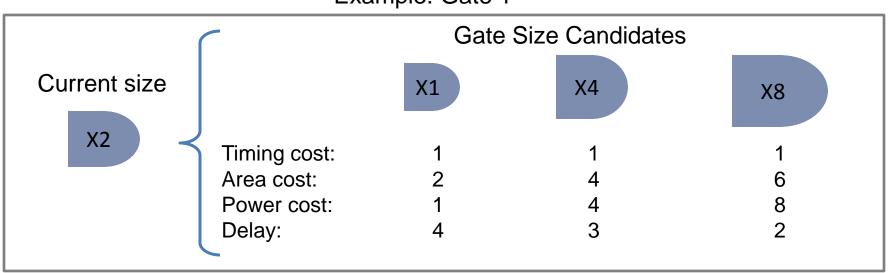

#### Example: Gate 1

### **ECO-cost aware design via LPECO**

minimize

$$\sum_{i,k} p_{ik} y_{ik} + \gamma_t \hat{c}_{\text{timing}}(\mathbf{y}; \mathbf{x}) + \gamma_a \hat{c}_{\text{area}}(\mathbf{y}; \mathbf{x})$$

subject to  $t_i + d_{i0} + \sum_k \delta_{ik} y_{ik} \le t_j, \quad \forall i \in \text{fo}(j)$  $t_i \le T_{\max}$

$$\sum_k y_{ik} \le 1, \quad \forall i$$

$0 \le y_{ik} \le 1$

t : arrival time for gate i  $d_{i0}$  : current delay for gate i  $\delta_{ik}$  : change in delay of gate i under size k  $y_{ik}$  : assignment variable of gate i to size k  $p_{ik}$  : change in leakage power of gate i to size k  $(\delta_{ik}, d_{i0})$  are from the commercial tool)

Example: Gate 1

| ſ                                                                | Gate Si                                                | ze Candidates                                                 |                                                               |

|------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|

| Current size                                                     | X1<br>$(y_{11} = 1)$                                   | X4                                                            | X8                                                            |

| X2<br>Timing cost:<br>Area cost:<br>Power cost:<br>Delay change: | $(y_{11} - 1)$ $1$ $2$ $-1 (p_{11})$ $4 (\delta_{11})$ | $(y_{14} = 1)$<br>1<br>4<br>3 $(p_{11})$<br>3 $(\delta_{14})$ | $(y_{18} = 1)$<br>1<br>6<br>7 $(p_{11})$<br>2 $(\delta_{18})$ |

### **Experimental Setup**

- 45nm Nangate Open Cell Library

- Manufacturing process change:

|                 | Nmos | Pmos |

|-----------------|------|------|

| $V_{ m th}$     | -10% | -5%  |

| t <sub>ox</sub> | +5%  | -5%  |

| $C_{\rm gate}$  | +10% | +10% |

| $l_{\rm eff}$   | +5%  | +5%  |

- ECO's are performed by a leading commercial design tool

- Runtime of LPECO ~.01 to 103s

### **Experimental Setup**

|                 | Nmos | Pmos |

|-----------------|------|------|

| $V_{ m th}$     | -10% | -5%  |

| t <sub>ox</sub> | +5%  | -5%  |

| $C_{\rm gate}$  | +10% | +10% |

| $l_{\rm eff}$   | +5%  | +5%  |

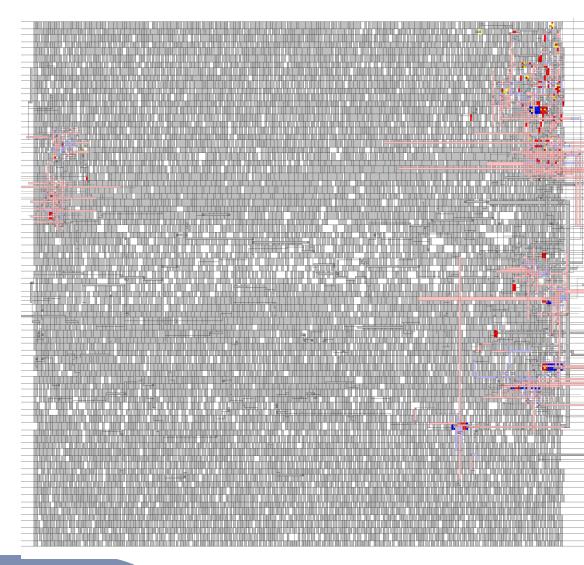

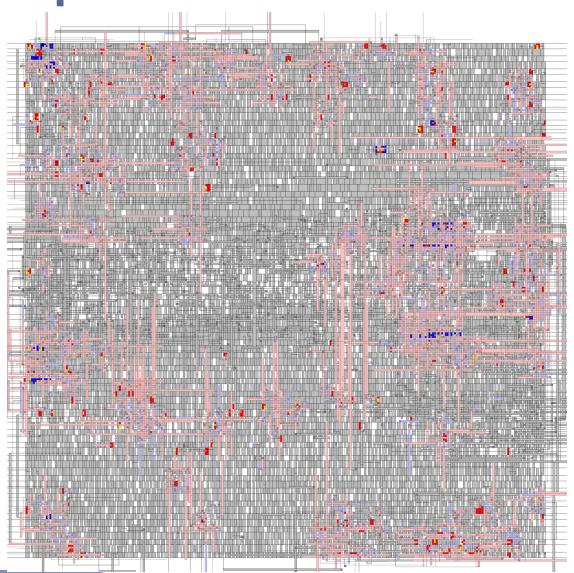

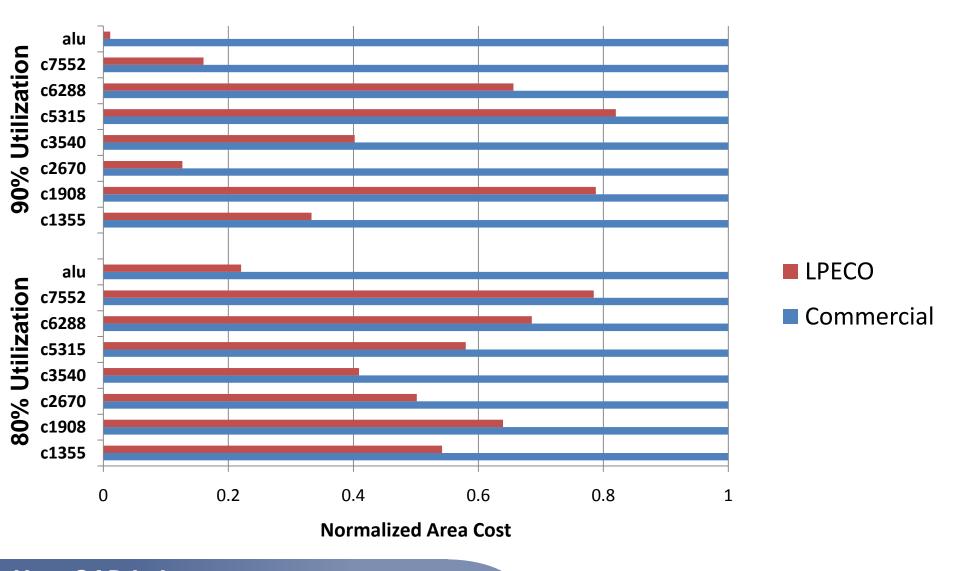

### **Results: Area Cost Comparison**

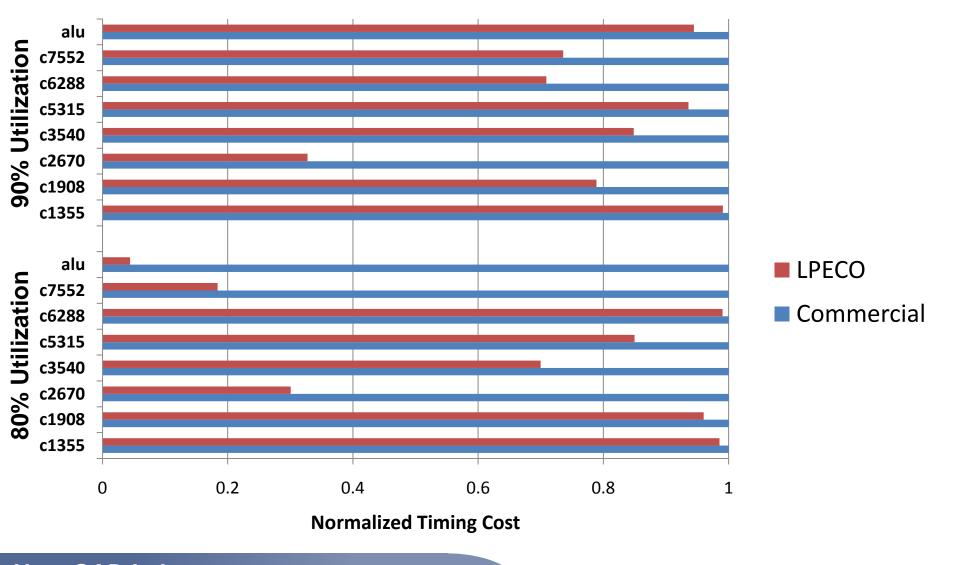

## **Results: Timing Cost Comparison**

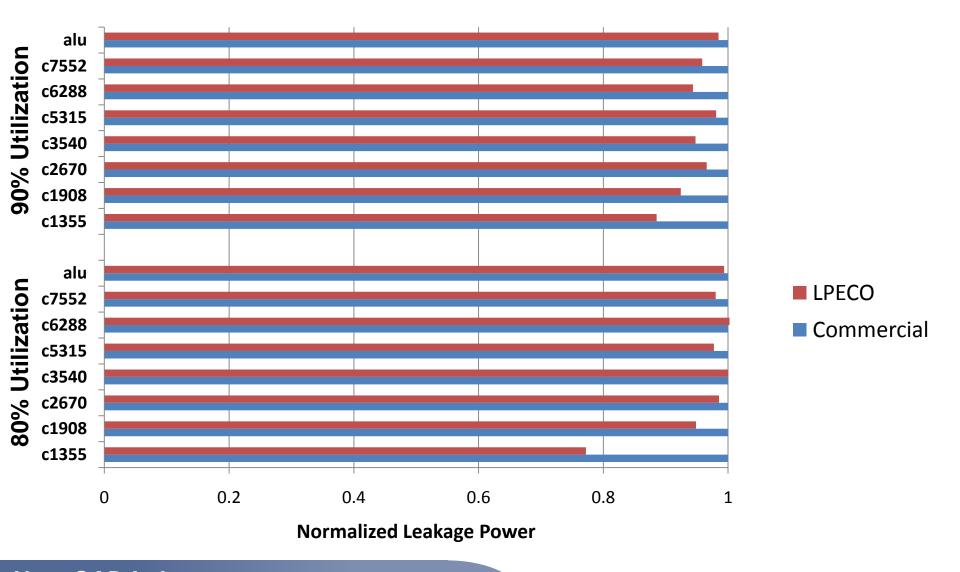

### **Results: Leakage Power**

21

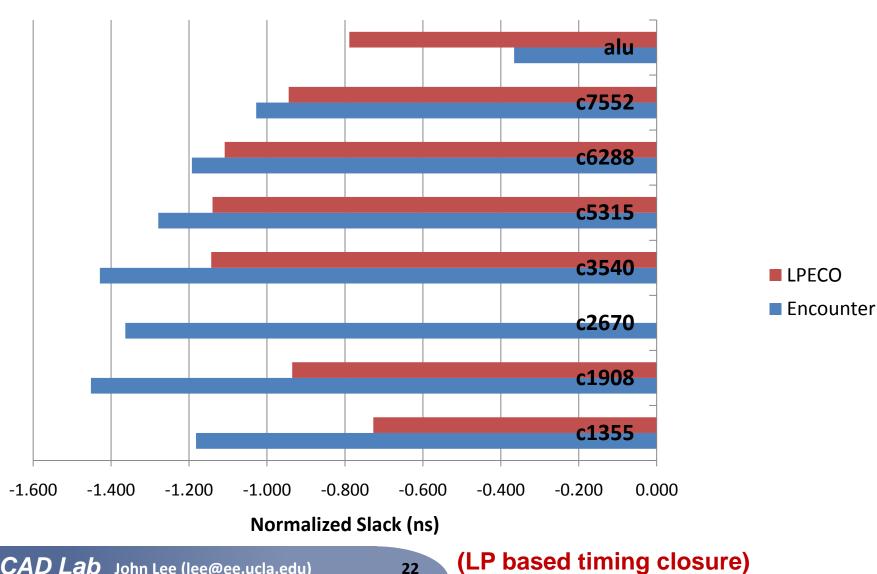

### **Results: Slack (Infeasible Cases)**

### Summary

- Quantified ECO Costs:

- ECO Timing Cost

- ECO Area Cost

- Performed incremental optimization to minimize ECO costs using LPECO

- Method performs well compared to commercial tool:

- 22% to 88% reduction in ECO Area

- 1% to 67% reduction in ECO Timing Cost

- Future goals:

- Initial designs that incur small ECO penalties in the future

- Large scale examples