## On Electrical Modeling of Imperfect Diffusion Patterning

Tuck-Boon Chan and <u>Puneet Gupta</u>\* Dept. of EE, University of California Los Angeles (<u>puneet@ee.ucla.edu</u>)

Work partly supported by IMPACT and SRC.

NanoCAD Lab

http://nanocad.ee.ucla.edu/

## Outline

- Motivation

- Modeling Diffusion Rounding

- Parameter Extraction

- Experimental Results

- Conclusions

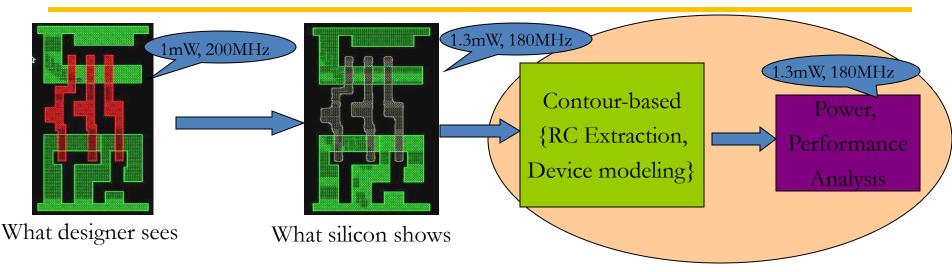

#### Lithographic WYSIWYG Breakdown

- Existing compact device models (e.g., BSIM) do not handle non-rectangular geometries.

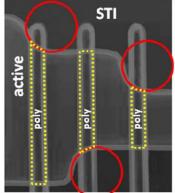

- Sources of diffusion rounding:

- Different channel widths with tight poly pitch

- Power/Ground diffusion straps

- Large poly-active corner spacing is required to avoid diffusion rounding → area overhead

Figure from V. Moroz, M. Choi, & X.W. Lin, *SPIE* 2009.

## **Previous Works**

- Modeled polysilicon rounding/line edge roughness only [SPIE'06, DAC'07, etc]

- Assumed current flows in horizontal direction

- Modeled non-rectangular gate device by slicing device's channel and connecting them in parallel

- Empirical diffusion rounding model [ASPDAC'08]

- Fitted  $I_{\mbox{\scriptsize on}}$  and  $I_{\mbox{\scriptsize off}}$  functions based on available data

- Did not model asymmetrical currents for drain/source side rounding

## **This Work**

- First Poly + diffusion rounding model.

Developed ground up from fundamental physics

- Models asymmetrical currents for drain/source side rounding.

SPICE-based calibration of the model

No need for silicon or TCAD simulation data.

# **Modeling Diffusion+Poly Rounding**

Extract parameters: •Channel width •Channel length •V<sub>th</sub>

Obtain total current using SPICE simulation

Equivalent W,L,V<sub>th</sub>

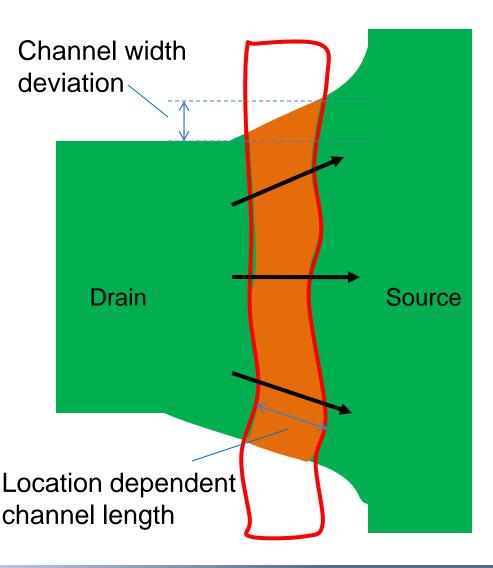

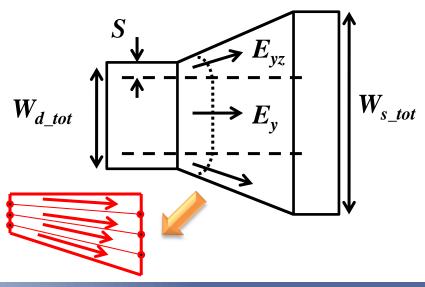

# **Channel Slicing**

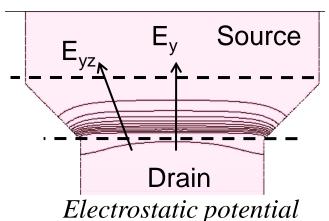

- Channel's electrostatic potential is two-dimensional

- Changes  $L_{\text{eff}}$  and  $W_{\text{eff}}$

- Strategy: divide channel into 3 sections.

- Assume E field is :

- > Purely horizontal in middle.

- Changing linearly from middle to edges.

TCAD simulation

# Slicing Guideline : 'S'

a, b and L<sub>eff-ref</sub> are technology independent parameters extracted from TCAD data

$a = 8nm, b = 0.089nm^{\circ^{-1}}$  and  $L_{\text{eff-ref}} = 25nm$

- θ and L<sub>eff</sub> are geometrical parameters extracted from device's shape

- Larger θ (larger source/drain widths) leads to stronger vertical (z) E-field and a larger S

- But increased source/drain is further away from channel  $\rightarrow$  vertical E-field and S weakly dependent on  $\theta$

- Horizontal(y) field changes linearly with channel length  $\rightarrow$  modeled as a multiplier, L<sub>eff</sub>/L<sub>eff-ref</sub>

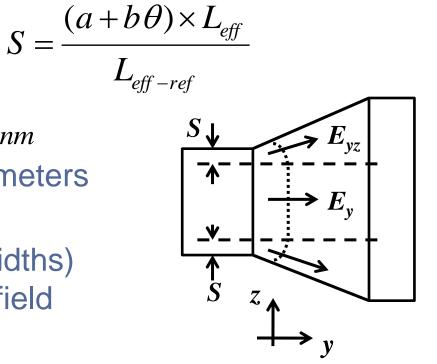

# **Effective Channel Length**

- Middle section of device's channel is sliced into small transistors with equal source and drain widths

- Source and drain of edge sections are divided into slices equally

- Assume E-field/current follows the direction of slices

- Effective channel length of each slice,  $L_{eff-i} = L_i$

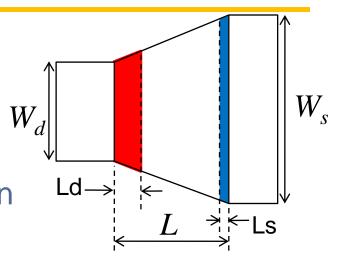

## **Effective Channel Width**

• Effective width of sliced channel

$$W_{eff} = \frac{(W_s - W_d)}{\ln(W_s / W_d)} \quad ( (W_s - W_d) ) \quad (W_s - W_d) \quad (W_s - W_d)$$

$W_{d\_i}$  and  $W_{s\_i}$  are obtained by approximating edges with straight lines orthogonal to the vector of channel length

•  $W_{eff}$  is derived based on gradual channel approximation  $\rightarrow$  voltage varies gradually from drain to source

$\begin{array}{lll} \mbox{Channel width} & \int_0^L \underbrace{I_D.dy}_{(W_d + (W_s - W_d)y/L)} = \int_{V_s}^{V_d} \mu Cox[V_G - V_{th} - V]dV \\ \mbox{channel} & I_D = \frac{1}{L} \frac{(W_s - W_d)}{\ln(W_s/W_d)} \mu Cox[V_G - V_{th} - \frac{V_{ds}}{2}]V_{ds}. \end{array}$

- Second order effects (DIBL, velocity saturation, etc.)

- Considered by applying effective length, width and  $V_{th}$  in SPICE simulation with BSIM model.

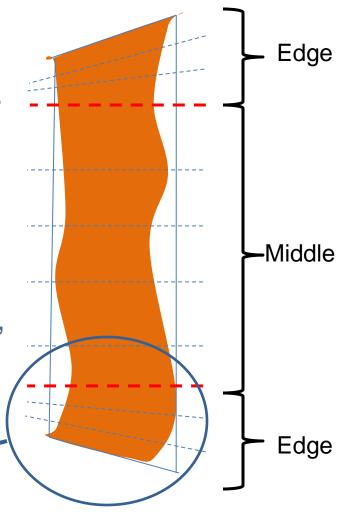

## **∆Vth - Narrow Width Effect (NWE)**

$$\Delta V_{th-\text{effective}} = \Delta V_{th-\text{Narrow width}} + \Delta V_{th-CS}$$

Non-uniform V<sub>th</sub> along channel width

- Impact of NWE is modeled by fitting  $\Delta V_{th}$  as a function of location [SPIE'06]

$$\Delta Vth(x) = \begin{cases} K_1(x-w)^2 + K_2(x-w) & 0 \le x \le w \\ 0 & w \le x \le W - w \\ K_1(W-x-w)^2 + K_2(W-x-w) & W-w \le x \le W \end{cases}$$

w is the maximum width affected by NWE W is device's average width  $K_1 = 1.65 (NMOS) 0.01 (PMOS)$  $K_2 = 1.65 (NMOS) 0.01 (PMOS)$ w = 5nm (NMOS) 1nm (PMOS) Fitted based on rectangular devices data

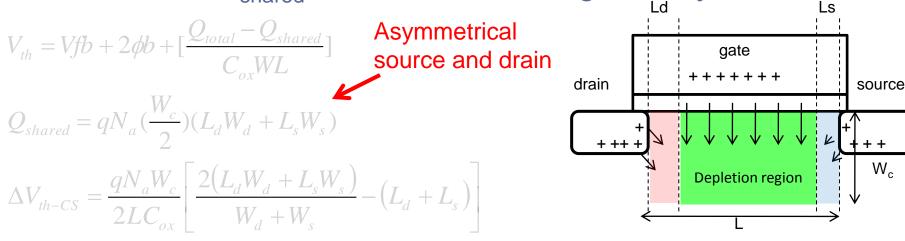

# **∆Vth – Asymmetrical Source/Drain**

- A portion of depletion region is shared between gate and source/drain

- Asymmetric source/drain sharing regions change effective region supported by gate alone → V<sub>th</sub> variation

- Charge Sharing Model :

- $\Delta V_{th} \alpha Q_{shared}$ ,

- Estimate Q<sub>shared</sub> based on device's geometry

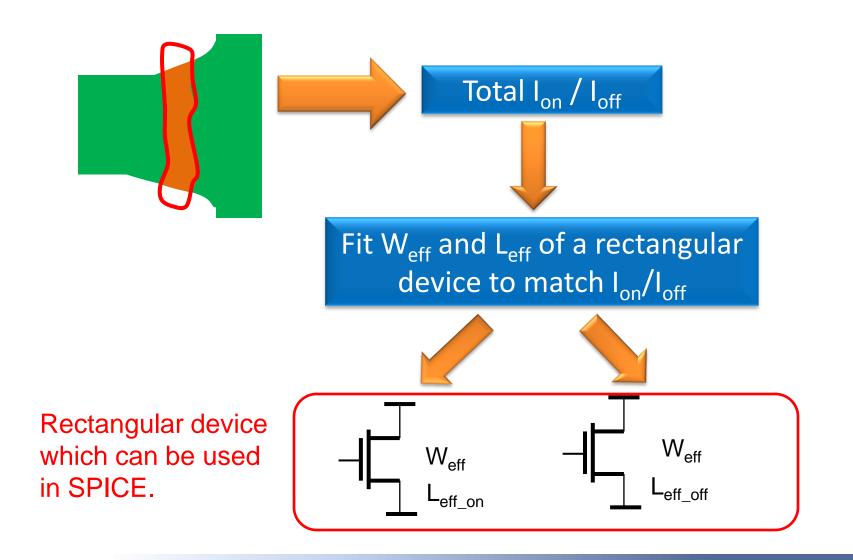

## **Total Currents**

Each slice can be represented by rectangular transistor with equivalent L,W and V<sub>th</sub>:

$$I_{total} = \sum_{i=1}^{n} f(L_i, W_i, Vth_i)$$

Can be obtained using conventional compact model e.g., (BSIM).

- Second order effects are implicitly considered in BSIM.

- Evaluate  $I_{total}$  at  $V_{gs}=0$ ,  $V_{ds}=V_{dd}$  (off)  $V_{gs}=V_{dd}$ ,  $V_{ds}=V_{dd}$  (on)

#### Equivalent Rectangular Transistor for Circuit Simulation

#### **Parameter Extraction**

- Channel length and width

Obtained directly from shapes.

- $\Delta V_{th} = \Delta V_{th-narrow width} + \Delta V_{th-cs}$

$$\Delta V_{th-CS} = \frac{qN_aW_c}{2LC_{ox}} \left[ \frac{2(L_dW_d + L_sW_s)}{W_d + W_s} - (L_d + L_s) \right]$$

Unknowns: charge sharing regions contributed by source and drain.

L<sub>d</sub> and L<sub>s</sub> can be calibrated using

Silicon data or TCAD simulation results

SPICE (+ BSIM) simulation results

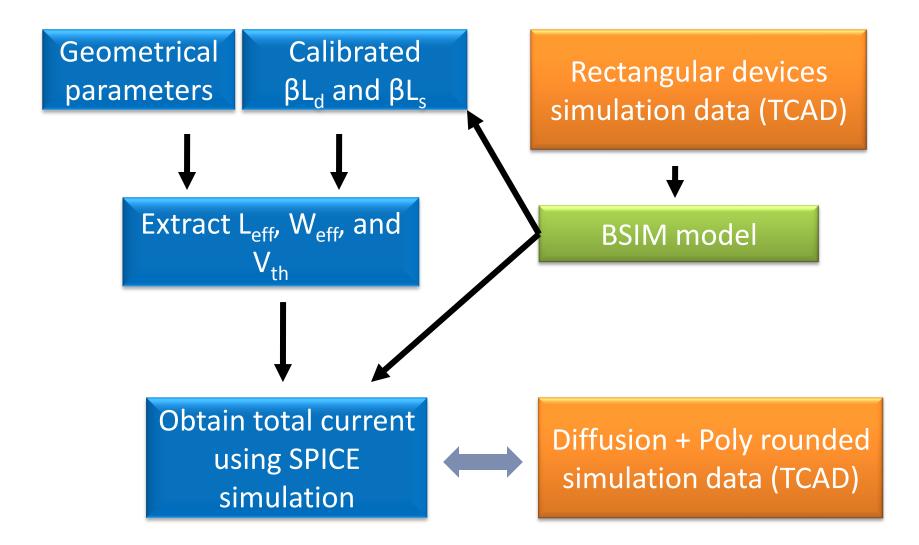

## **TCAD-Based Calibration**

- Require I<sub>off</sub> of a diffusion rounded device (forward and reverse bias)

- L<sub>d</sub> and L<sub>s</sub> are calibrated to minimize error between model and measured I<sub>off</sub>

- $I_{off}$  is used for calibration as it is sensitive to  $V_{th}$  variation caused by  $L_d$  and  $L_s$  $L_d=5 \text{ nm}$  (NMOS) 5.5 nm (PMOS)  $L_s=1 \text{ nm}$  (NMOS) 1.0 nm (PMOS)

## **SPICE Based Parameter Extraction**

- Extract L<sub>d</sub> and L<sub>s</sub> from rectangular devices.

- Perturb L and  $V_{ds}$  to obtain  $\Delta V_{th}$ , Let  $K_1 = V_{th,L1} - V_{th,L2}$  Eq. 1  $K_2 = V_{th} |_{V_{th}} - V_{th} |_{V_{th}}$  Eq. 2

$L_d$  and  $L_s$  are not fully extracted but they can be substituted into  $\Delta V$ th equation directly

$$K_{2} = V_{th} |_{V_{ds}=V_{dd}} -V_{th} |_{V_{ds}=0}$$

Eq. 2

$$\frac{qN_{a}W_{c}}{C_{ox}}(L_{d}) = K_{1}(\frac{L_{1}L_{2}}{L_{1}-L_{2}}) - \frac{K_{2}L_{1}}{2}$$

Combine

Eq. 1 and Eq.2

$$\frac{qN_{a}W_{c}}{C_{ox}}(L_{s}) = K_{1}(\frac{L_{1}L_{2}}{L_{1}-L_{2}}) + \frac{K_{2}L_{1}}{2}$$

- Extract parameters at large length and width to decouple second order effects

- Less accurate compared to TCAD based calibration as  $L_d$ and  $L_s$  are not extracted  $\rightarrow$  cannot evaluate source/drain widths in charge sharing region  $\rightarrow$  approximate them as source/drain widths at junctions.

## **Simulation Setup**

| Parameters               | Value                | DopingConcentration [cm^-3]<br>2.5E+18<br>2.0E+15<br>1.5E+12 |

|--------------------------|----------------------|--------------------------------------------------------------|

| Drawn gate length        | 45 nm                | -1,9E+14<br>-2,4E+17<br>-3,0E+20                             |

| Effective channel length | 25 nm                |                                                              |

| Width (NMOS/PMOS)        | 110-300 / 255-500 nm |                                                              |

| Vdd                      | 1 V                  |                                                              |

| Тох                      | 1.5 nm               |                                                              |

| S/D doping (NMOS/PMOS)   | 3e20 / 2e20 cm-3     | DopingConcentr<br>2.5E+18<br>2.0E+15                         |

| NSUB (NMOS/PMOS)         | 2.5e18 / 2.5e18 cm-3 | 2.0E+15<br>1.5E+12<br>-1.9E+14<br>-2.4E+17                   |

| Junction depth           | 20 nm                | -3.0E+20                                                     |

| Line-end extension       | 20 nm                |                                                              |

| Spacer width             | 30 nm                |                                                              |

0.3

0.35

0.4

0.45

#### TCAD : Sentaurus 3D

## **Experiment Flow (SPICE calibrated)**

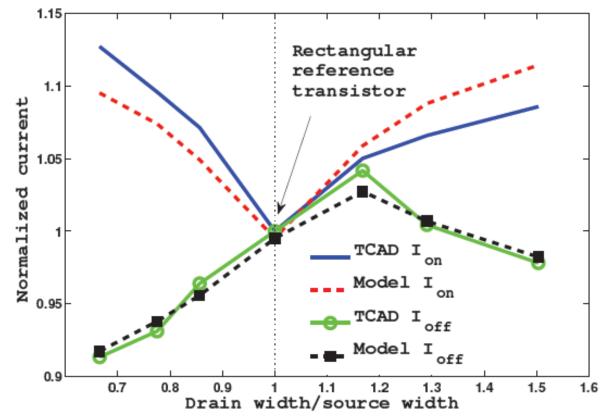

#### **TCAD vs Model (Diffusion Rounding only)**

- Asymmetrical I<sub>on</sub>/I<sub>off</sub> when rounding happens on Drain/Source terminals

- $\Delta V$ th varies according to drain/source ratio.

# **Poly+Diffusion Rounding**

|                      |             |       |                                         |                                         |                                         |                 |                  |                 |                  |                       | $L_{I}$         | $\longleftrightarrow$ |                   |

|----------------------|-------------|-------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------|------------------|-----------------|------------------|-----------------------|-----------------|-----------------------|-------------------|

|                      | 11          | 1.2   |                                         |                                         |                                         | Error (%)       |                  |                 | W <sub>1</sub>   |                       |                 |                       |                   |

|                      | L1 $ $ (nm) | L2    | W <sub>d</sub>                          | $W_1$                                   | $W_2$                                   | TCAE            | ) cal.           | SPICE           | Ecal.            |                       | drain           | ſ                     | source            |

|                      | (()))       | (())) | ((((((((((((((((((((((((((((((((((((((( | ((((((((((((((((((((((((((((((((((((((( | ((((((((((((((((((((((((((((((((((((((( | I <sub>on</sub> | I <sub>off</sub> | I <sub>on</sub> | I <sub>off</sub> | Wd                    |                 |                       |                   |

| Diffusion rounding   | 45          | 45    | 155                                     | 26                                      | 0                                       | -2.1            | -0.8             | -2.0            | -0.5             |                       |                 |                       |                   |

| only                 | 45          | 45    | 155                                     | 45                                      | 0                                       | -2.0            | 0.7              | -1.9            | 1.1              | <i>W</i> <sub>2</sub> |                 |                       | <b>1</b>          |

| (Source side larger) | 45          | 45    | 155                                     | 78                                      | 0                                       | -2.8            | 0.4              | -2.7            | 0.7              |                       | <del>&lt;</del> |                       | $\rightarrow L_2$ |

| Poly rounding only   | 55          | 45    | 155                                     | 0                                       | 0                                       | NA              | NA               | -0.7            | 2.5              |                       |                 |                       |                   |

|                      | 35          | 45    | 155                                     | 0                                       | 0                                       | NA              | NA               | -0.2            | 7.5              |                       |                 |                       |                   |

|                      | 55          | 45    | 155                                     | 45                                      | 0                                       | NA              | NA               | -1.4            | 3.1              |                       |                 |                       |                   |

| Poly+ diffusion      | 55          | 45    | 155                                     | 0                                       | 45                                      | NA              | NA               | -2.8            | -2.7             |                       |                 |                       |                   |

| rounding             | 35          | 45    | 155                                     | 45                                      | 0                                       | NA              | NA               | -2.4            | 0.7              |                       |                 |                       |                   |

|                      | 35          | 45    | 155                                     | 0                                       | 45                                      | NA              | NA               | -0.7            | 7.8              |                       |                 |                       |                   |

Average error :

(Diffusion layer rounding only) TCAD calibrated model = 1.6% SPICE calibrated model = 1.7% (Poly+ Diffusion layers rounding) SPICE calibrated model =2.7%

TIA

•

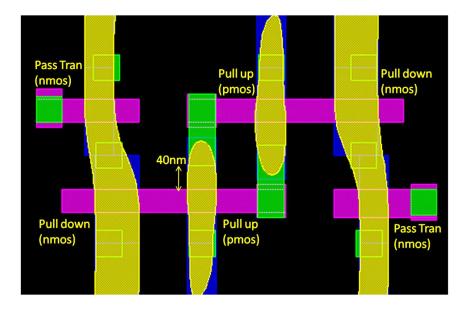

# **Diffusion Rounding on SRAM**

| Defocus<br>(nm) | Contact/Poly<br>Spacing (nm) | Overlay<br>(nm) | SNM<br>(mV) |

|-----------------|------------------------------|-----------------|-------------|

| 0               | 40                           | 0               | 378.20      |

| 0               | 20                           | 0               | 379.30      |

| 100             | 40                           | 0               | 376.50      |

| 100             | 20                           | 0               | 378.70      |

| 0               | 40                           | 20              | 377.10      |

SNM for rectangular device =378.40mV

- Diffusion rounding is not significant on SRAM.

- Second order effects are ignored (AS, PS, AD and PD)

- Symmetrical layout suppresses SNM variation.

- Results may vary for different optical model and device.

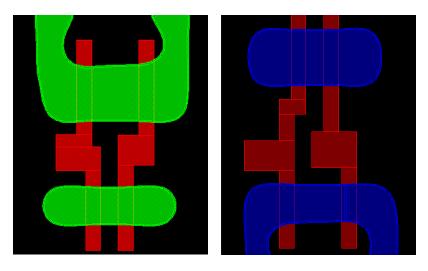

# **Application on Logic Cells**

|         |                       | NAND_X1  |         | NOR_X1   |         |

|---------|-----------------------|----------|---------|----------|---------|

|         |                       | Original | · · ·   | Original | Spacing |

|         |                       |          | Reduced |          | Reduced |

| Delay   | nominal (no defocus)  | 1.00     | 1.00    | 1.00     | 0.99    |

|         | worst (100nm defocus) | 1.05     | 1.04    | 1.05     | 1.05    |

| Leakage | nominal (no defocus)  | 1.00     | 1.00    | 1.00     | 1.01    |

|         | worst (100nm defocus) | 0.91     | 0.91    | 0.90     | 0.90    |

|         | area                  | 1.00     | 0.95    | 1.00     | 0.95    |

- At 100nm defocus

△ Delay = 5%

△ Leakage = 9%

- Design rule can be optimized.

NAND2\_X1 NOR2\_X1

## Sources of inaccuracies

- 1. Source/drain widths of charge sharing regions vary according to  $L_d$  and  $L_s$ . Exact  $L_d$  and  $L_s$  are not decoupled in SPICE-based calibration

- 2. Drain side width changes when device is under saturation

- 3. Piece wise modeling error in channel's electric field distribution

## Future work

- Captures channel width variation in saturation by estimating channel length modulation

- Extract capacitance related parameters :

- Diffusion area and perimeter (AD,PD,AS & PS in BSIM)

## Conclusions

- Diffusion rounding affects channel length, width and  $V_{\text{th}}.$

- Modeling error for poly+diffusion rounding are 2.3% (I\_{on}) and 1.0% (I\_{off})

- Model can be calibrated using SPICE.

- Applications:

- Post-lithography circuit analysis.

- Design rules exploration.