UNIVERSITY OF CALIFORNIA

Los Angeles

# Design Enablement and Design-Centric Assessment of Future Semiconductor Technologies

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical Engineering

by

# Rani Abou Ghaida

© Copyright by Rani Abou Ghaida 2012

#### Abstract of the Dissertation

# Design Enablement and Design-Centric Assessment of Future Semiconductor Technologies

by

#### Rani Abou Ghaida

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2012 Professor Puneet Gupta, Chair

The semiconductor industry is likely to see several radical changes in the manufacturing, device and interconnect technologies in the next few years and decades. One of the most favorable options of manufacturing technologies is multiple-patterning lithography. This novel technology has serious implications on design, however, and it will require an enabling design to see any adoption.

This dissertation contributes to the design enablement of multiple-patterning technology. We propose a general methodology for the automated adaptation of layout to multiple-patterning masking the complexity in dealing with its manufacturing constraints. We also study the impact of this technology on design and show the benefits of bringing the design perspective into making manufacturing-process decisions. Lastly, we propose a novel technique for DP that reduces cost and improve overlay/Critical-Dimension (CD) control in multiple-patterning.

Many technology choices are presented to achieve scaling to every next node and early technology assessment, before the actual development of technologies, has become more necessary than ever as a means to ensure faster adoption and manageable technology/design development costs. Technology assessment is currently a highly unsystematic procedure that relies on small-scale experiments and manufacturing tests and much on speculations based on technologists/designers experience with previous technology generations. This dissertation also addresses the problem of increasing complexity in making technological decisions. It aims at the development of a computation infrastructure for the systematic and early assessment of technologies and their impact on circuit design. The infrastructure is the first of its kind and is expected to have a lasting impact on technology development. The infrastructure allows for true exploration of design and technology choices, thereby redirecting research and development efforts toward options that are more likely to eventually see adoption. Finally, the infrastructure is applied to evaluate multiple-patterning process decisions and study their implications on design. The dissertation of Rani Abou Ghaida is approved.

Jingsheng Jason Cong

Lei He

Dejan Markovic

Puneet Gupta, Committee Chair

University of California, Los Angeles

2012

To Said, Nabila, Houssam, Rania, and Hikmat ...

### TABLE OF CONTENTS

| 1  | Intr           | oducti | ion                                                   | 1  |

|----|----------------|--------|-------------------------------------------------------|----|

|    | 1.1            | Scalin | g in the Sub-wavelength Lithography Regime            | 2  |

|    |                | 1.1.1  | Multiple-Patterning Lithography                       | 3  |

|    | 1.2            | Design | n/Manufacturing Interactions                          | 7  |

|    |                | 1.2.1  | Design Rules                                          | 7  |

|    |                | 1.2.2  | Design Enablement                                     | 7  |

|    | 1.3            | Proble | em Statement                                          | 9  |

|    | 1.4            | Objec  | tive and Scope of this Thesis                         | 12 |

|    |                |        |                                                       |    |

| Ι  | $\mathbf{Des}$ | ign E  | nablement of Multiple-Patterning Technology           | 14 |

| 2  | Lou            | out D  | ecomposition and Legalization for Multiple-Patterning |    |

|    | v              |        |                                                       | 15 |

| Τ¢ |                |        |                                                       |    |

|    | 2.1            | DP Co  | oloring                                               | 17 |

|    |                | 2.1.1  | Prior Art in DP Coloring                              | 18 |

|    |                | 2.1.2  | Overview of Our DP Coloring Approach                  | 20 |

|    |                | 2.1.3  | Multiple Spacing-Rules Projection                     | 21 |

|    |                | 2.1.4  | Coloring Objectives                                   | 21 |

|    |                | 2.1.5  | Implementation Details                                | 23 |

|    |                | 2.1.6  | Stitches vs. Conflicts and Special Cases              | 27 |

|    |                | 2.1.7  | Coloring Results                                      | 28 |

|    | 2.2            | TP Co  | ploring                                               | 32 |

|    |                | 2.2.1  | Prior Art in TP Coloring                              | 34 |

|    |                | 2.2.2  | Overview of Our Approach                              | 35 |

|     | 2.2.3                    | Description of the Proposed Methodology for TP Coloring $\ .$ .                                                                                                                                                                                                                                                        | 36                               |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|     | 2.2.4                    | Experimental Results                                                                                                                                                                                                                                                                                                   | 39                               |

| 2.3 | Layou                    | t Legalization for MP                                                                                                                                                                                                                                                                                                  | 45                               |

|     | 2.3.1                    | Prior Art in DP Conflict-Removal                                                                                                                                                                                                                                                                                       | 45                               |

|     | 2.3.2                    | Our Approach – Legalization with Minimum Layout Pertur-                                                                                                                                                                                                                                                                |                                  |

|     |                          | bation                                                                                                                                                                                                                                                                                                                 | 47                               |

|     | 2.3.3                    | Layout Simplification for More Efficient DP Conflict Removal                                                                                                                                                                                                                                                           | 50                               |

|     | 2.3.4                    | DP-Compatible Design                                                                                                                                                                                                                                                                                                   | 54                               |

|     | 2.3.5                    | Experimental Setup and Results                                                                                                                                                                                                                                                                                         | 56                               |

| Ove | erlay In                 | npact for Design in Metal Double-Patterning                                                                                                                                                                                                                                                                            | 62                               |

| 3.1 | Electr                   | ical Impact of Within-Layer Overlay                                                                                                                                                                                                                                                                                    | 65                               |

|     | 3.1.1                    | Overlay Modeling                                                                                                                                                                                                                                                                                                       | 65                               |

|     | 3.1.2                    | Capacitance Model                                                                                                                                                                                                                                                                                                      | 66                               |

|     | 3.1.3                    | Electrical Impact in Positive DP                                                                                                                                                                                                                                                                                       | 66                               |

|     | 3.1.4                    | Electrical Impact in Negative DP                                                                                                                                                                                                                                                                                       | 68                               |

| 3.2 | Exper                    | imental Methodology and Results                                                                                                                                                                                                                                                                                        | 69                               |

|     | 3.2.1                    | Experimental Setup                                                                                                                                                                                                                                                                                                     | 69                               |

|     | 3.2.2                    | Evaluation Methodology                                                                                                                                                                                                                                                                                                 | 72                               |

|     | 3.2.3                    | Results                                                                                                                                                                                                                                                                                                                | 72                               |

| 3.3 | Obser                    | vations and Implications for Design                                                                                                                                                                                                                                                                                    | 73                               |

|     | 3.3.1                    | Results Analysis and Relative Importance of Overlay Sources .                                                                                                                                                                                                                                                          | 73                               |

|     | 3.3.2                    | Effects of Design Parameters                                                                                                                                                                                                                                                                                           | 75                               |

|     | 3.3.3                    | Expected Worst-Case Overlay Impact in Critical Path                                                                                                                                                                                                                                                                    | 77                               |

|     | 3.3.4                    | Overlay Impact on Crosstalk Noise                                                                                                                                                                                                                                                                                      | 82                               |

|     | 3.3.5                    | Estimation of Overlay Requirement                                                                                                                                                                                                                                                                                      | 83                               |

|     | <b>Ove</b><br>3.1<br>3.2 | 2.2.4<br>2.3 Layou<br>2.3.1<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.3<br>2.3.4<br>2.3.4<br>2.3.5<br><b>Overlay In</b><br>3.1.1<br>3.1.2<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2<br>3.1.3<br>3.1.4<br>3.2<br>3.1.3<br>3.1.4<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3<br>3.3<br>Obser<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | 2.2.4       Experimental Results |

|    | 3.4   | Explo   | ring Processing Options                                                          | . 84  |

|----|-------|---------|----------------------------------------------------------------------------------|-------|

| 4  | Sing  | gle-Ma  | sk Double-Patterning Lithography                                                 | 88    |

|    | 4.1   | Shift-7 | Frim DP Overview and Layout Restrictions                                         | . 91  |

|    |       | 4.1.1   | Manufacturing Process                                                            | . 91  |

|    |       | 4.1.2   | STDP Challenges and Downsides                                                    | . 93  |

|    |       | 4.1.3   | Layout Restrictions at Poly-line Layer                                           | . 93  |

|    |       | 4.1.4   | Layout Restrictions at Contacts Layer                                            | . 96  |

|    | 4.2   | STDP    | Design Implementation                                                            | . 98  |

|    |       | 4.2.1   | Limitation on Pitch Relaxation of Double Patterning $\ldots$                     | . 98  |

|    |       | 4.2.2   | Poly-line STDP Standard-Cell Library and Mask Layout Generation                  | . 99  |

|    |       | 4.2.3   | Poly-line Plus Contacts STDP Standard-Cell Library and Mask<br>Layout Generation |       |

|    | 4.3   | STDP    | Benefits                                                                         | . 110 |

|    |       | 4.3.1   | Overlay and Throughput Benefits                                                  | . 110 |

|    |       | 4.3.2   | Alleviating CD Bimodality Problem                                                | . 111 |

|    |       | 4.3.3   | Comparison with Popular Double-Patterning Technologies .                         | . 112 |

| II | De    | sign-(  | Centric Assessment of Technology                                                 | 115   |

| 5  | A F   | ramew   | ork for Early Co-Evaluation of Design Rules, Technolog                           | у     |

| Cl | hoice | s, and  | Layout Methodologies                                                             | 116   |

|    | 5.1   | Area I  | Estimation                                                                       | . 120 |

|    |       | 5.1.1   | Layout Topology Generation                                                       | . 120 |

|    |       | 5.1.2   | Tweaking Pairing                                                                 | . 124 |

|    |       | 5.1.3   | Routing Estimation                                                               | . 125 |

|   |                   | 5.1.4                                                                          | Congestion Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|-------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                   | 5.1.5                                                                          | Area Increase Due to Congestion                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                   | 5.1.6                                                                          | Runtime and Validation of Area Estimation                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.2               | Manut                                                                          | facturability Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 5.3               | Varial                                                                         | pility Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 5.4               | Exper                                                                          | imental Setup and Results                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                   | 5.4.1                                                                          | Testing Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                   | 5.4.2                                                                          | Evaluation of Poly-Patterning Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                   | 5.4.3                                                                          | Evaluation of Layout Styles                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                   | 5.4.4                                                                          | Assessment of Technologies and Wiring Schemes                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                   | 5.4.5                                                                          | DR Comparison of Different Processes                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                   | 5.4.6                                                                          | DR Exploration                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                   |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6 | $\mathbf{Exp}$    | oloratio                                                                       | on of Design Rules for Multiple-Patterning Technologies156                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 | <b>Exp</b><br>6.1 |                                                                                | on of Design Rules for Multiple-Patterning Technologies156<br>hodology for the Early Exploration of Design Rules for Multiple-                                                                                                                                                                                                                                                                                                                                        |

| 6 | -                 | A Met                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6 | -                 | A Met                                                                          | hodology for the Early Exploration of Design Rules for Multiple-                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6 | -                 | A Met<br>Patter                                                                | hodology for the Early Exploration of Design Rules for Multiple-                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6 | -                 | A Met<br>Patter<br>6.1.1                                                       | hodology for the Early Exploration of Design Rules for Multiple-<br>rning Technologies                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | -                 | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3                                     | hodology for the Early Exploration of Design Rules for Multiple-<br>rning Technologies                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | 6.1               | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3<br>A Met                            | hodology for the Early Exploration of Design Rules for Multiple-         ming Technologies       157         Probabilistic Layout and Congestion Estimation       159         DP Conflict Prediction Using Machine Learning       166         DP Design-Rule Exploration       171                                                                                                                                                                                    |

| 6 | 6.1               | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3<br>A Met                            | hodology for the Early Exploration of Design Rules for Multiple-<br>rning Technologies                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | 6.1               | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3<br>A Met<br>and O                   | hodology for the Early Exploration of Design Rules for Multiple-         rning Technologies       157         Probabilistic Layout and Congestion Estimation       159         DP Conflict Prediction Using Machine Learning       166         DP Design-Rule Exploration       171         thodology for Exploring the Interaction Between Design Rules       176         verlay Control       176                                                                   |

| 6 | 6.1               | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3<br>A Met<br>and O<br>6.2.1          | hodology for the Early Exploration of Design Rules for Multiple-         ming Technologies       157         Probabilistic Layout and Congestion Estimation       159         DP Conflict Prediction Using Machine Learning       166         DP Design-Rule Exploration       171         thodology for Exploring the Interaction Between Design Rules       176         Design Rules and Overlay Interaction       178                                              |

| 6 | 6.1               | A Met<br>Patter<br>6.1.1<br>6.1.2<br>6.1.3<br>A Met<br>and O<br>6.2.1<br>6.2.2 | hodology for the Early Exploration of Design Rules for Multiple-         ming Technologies       157         Probabilistic Layout and Congestion Estimation       159         DP Conflict Prediction Using Machine Learning       166         DP Design-Rule Exploration       171         thodology for Exploring the Interaction Between Design Rules       176         Design Rules and Overlay Interaction       178         Overlay and Yield Modeling       179 |

| 7.1    | Research Contributions | . 187 |

|--------|------------------------|-------|

| 7.2    | Future Research        | . 189 |

| Refere | nces                   | 192   |

### LIST OF FIGURES

| 1.1 | Abrupt poly line-ends formed using the trim exposure of a DP process       |    |

|-----|----------------------------------------------------------------------------|----|

|     | at 45nm technology node (reprinted from [ACC08])                           | 4  |

| 1.2 | Example of pitch-split DP, where dark-colored features were formed         |    |

|     | with one exposure and light-colored features were formed with a sec-       |    |

|     | ond exposure (reprinted from [Mac08])                                      | 4  |

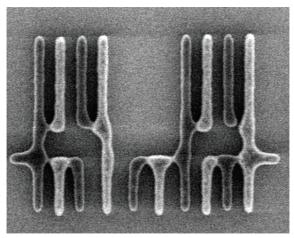

| 1.3 | Process flows for the different approaches of double-patterning (reprinted |    |

|     | from [ITRa]).                                                              | 5  |

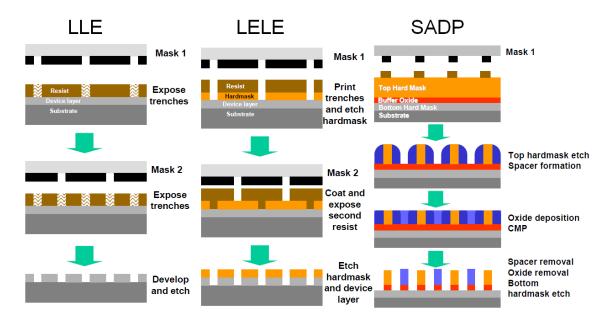

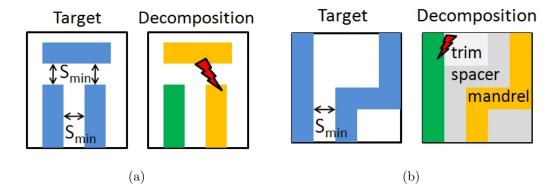

| 1.4 | Examples of a LELE/LLE forbidden pattern (a) and a SADP for-               |    |

|     | bidden pattern (b). $S_{min}$ denotes the minimum spacing of single-       |    |

|     | patterning and mandrel denotes layout features that do not appear          |    |

|     | on the mask of the first exposure                                          | 6  |

| 1.5 | Example of a regular fabric, which implements the function $!(AB+C)$       |    |

|     | (reprinted from [LPH09])                                                   | 8  |

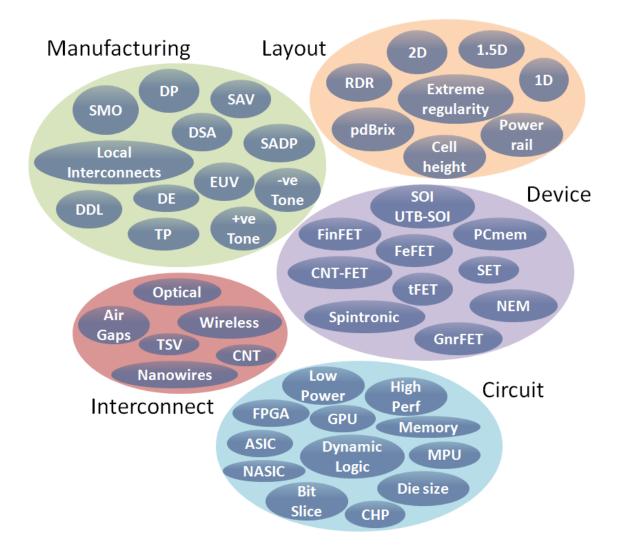

| 1.6 | Possible technology choices for the scaling to future technology gen-      |    |

|     | erations.                                                                  | 10 |

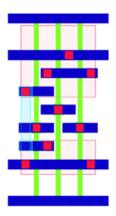

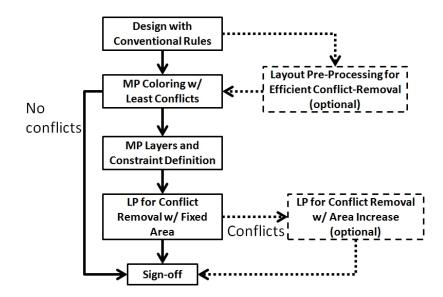

| 2.1 | The flow for our proposed method to achieve MP-enabled layout design.      | 17 |

| 2.2 | Example of a layout with odd cycle in its conflict graph (a) that was      |    |

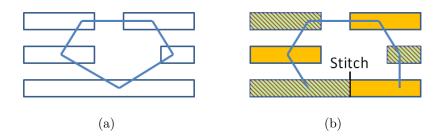

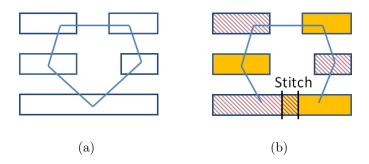

|     | broken by introducing a stitch (b)                                         | 18 |

| 2.3 | Illustration of the drawbacks of segmenting the layout into rectangles,    |    |

|     | which is performed in prior art of DP coloring and conflict removal        | 19 |

| 2.4 | DR-dependent projection to identify violating parts and stitch loca-       |    |

|     | tions. Violating parts are the blue features and non-violating parts       |    |

|     | are the clear features                                                     | 20 |

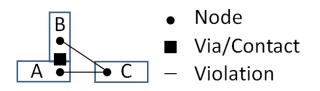

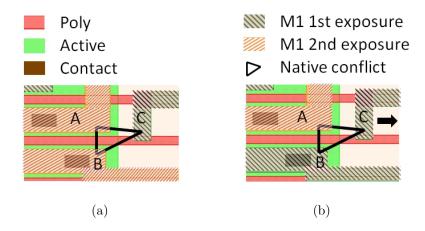

| 2.5  | Odd cycle coloring can affect the efficiency of conflict removal. In (a),        |    |

|------|----------------------------------------------------------------------------------|----|

|      | the conflict is on M1 between shapes A and B and can only be fixed               |    |

|      | if the gates are spaced apart and area is increased; in (b), the conflict        |    |

|      | is on M1 between shapes B and C and can be fixed by moving C in                  |    |

|      | the direction of the arrow without increasing area                               | 22 |

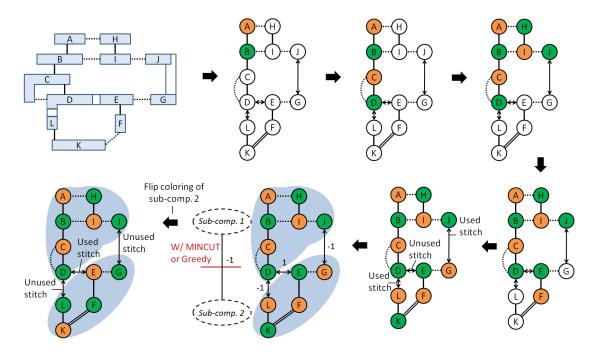

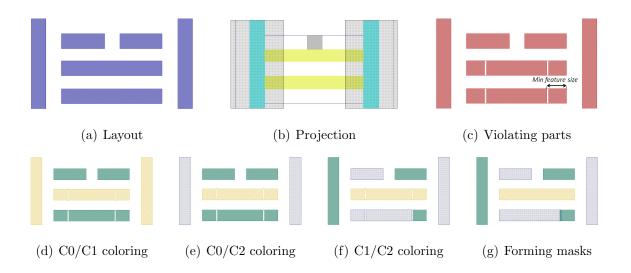

| 2.6  | An illustrating example showing each step of the coloring process for            |    |

|      | an isolated region of the layout                                                 | 23 |

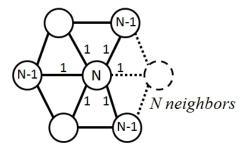

| 2.7  | ${\cal O}(n)$ coloring procedure with greedy algorithm for color-flipping^2.<br> | 25 |

| 2.8  | Case of most suboptimal solution for greedy-based flipping                       | 26 |

| 2.9  | Example showing two coloring solutions that our method may give                  |    |

|      | for the same layout (rare case with all diagonal violations) depending           |    |

|      | on the propagation order of the coloring: (a) with two DP violations             |    |

|      | and (b) with a single DP violation.                                              | 28 |

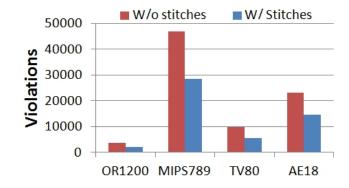

| 2.10 | Comparison of the number of same-color spacing violations when                   |    |

|      | stitches are forbidden and when they are allowed. $\ldots$                       | 31 |

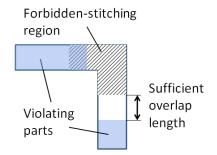

| 2.11 | Region of forbidden stitching at corner, which will be merged with               |    |

|      | the overlapping violating part on the left to prevent stitching at the           |    |

|      | corner. Note if the overlap length in the non-violating part is smaller          |    |

|      | than the minimum rule, the non-violating part will also be merged                |    |

|      | with the violating parts and no candidate stitches will be available in          |    |

|      | this shape                                                                       | 31 |

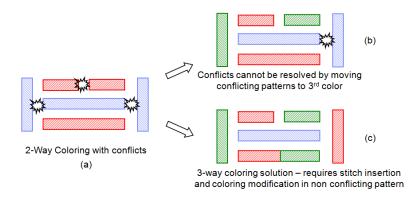

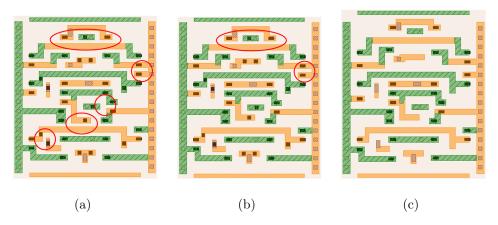

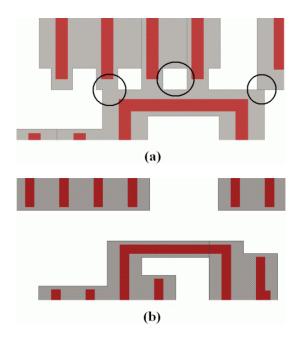

| 2.12 | (a) Example layout coloring with two colors showing conflicts, (b)               |    |

|      | TP layout coloring with the ILP approach and the naive approach                  |    |

|      | of using the third color to resolve conflicts, and (c) a conflict-free           |    |

|      | solution for TP coloring                                                         | 35 |

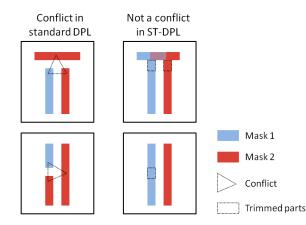

| 2.13 Example illustrating the application the different steps involved in     |   |

|-------------------------------------------------------------------------------|---|

| our triple-patterning coloring methodology. In (b), T2S violations            |   |

| are expanded and the parts of the target layout that are covered after        |   |

| the expansion are the T2S violating parts. T2T and S2S violating              |   |

| parts are identified similarly                                                | 6 |

| 2.14 The flow for our the proposed TP coloring method that uses multiple      |   |

| steps of DP coloring                                                          | 7 |

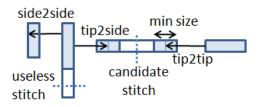

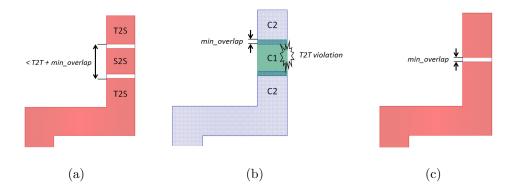

| 2.15 Illustrating example showing (a) candidate stitch at interface of S2S    |   |

| violating parts with other types of violating parts, (b) coloring prob-       |   |

| lem that occurs with insertion of candidate stitch locations at inter-        |   |

| face, and (c) solving the problem by inserting a single stitch at center      |   |

| of S2S violating parts with length smaller than T2T (or T2S if larger)        |   |

| plus two times the minimum mask overlap length                                | 8 |

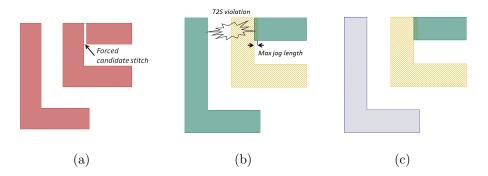

| 2.16~ Illustrating example of the coloring of an U-shape violating part show- |   |

| ing (a) forced candidate stitch insertion to separate the two segments        |   |

| of the U-shape, (b) the coloring problem that may occur once the              |   |

| coloring of violating parts and the mask-layouts are formed, and (c)          |   |

| fixing the coloring with an extra coloring step post coloring of violat-      |   |

| ing parts                                                                     | 9 |

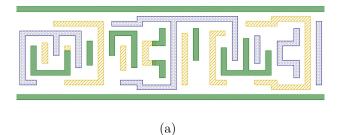

| 2.17 Layout snippets of results of the proposed TP coloring methodology       |   |

| when applied to standard-cell library designs at (a) 14nm with regular        |   |

| bidirectional M1 and (b) 22nm with more complex bidirectional M1 $$ 4         | 0 |

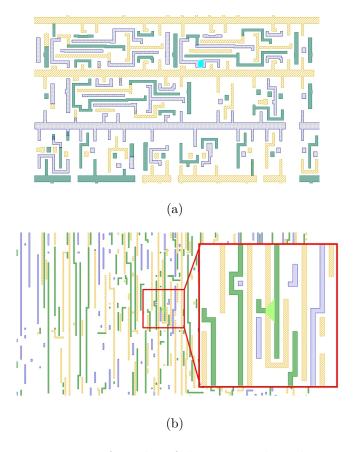

| 2.18 Layout snippets of results of the proposed TP layout coloring method-    |   |

| ology when applied to full-design layouts at (a) 45nm with irregular          |   |

| bidirectional M1 and (b) 32nm with bidirectional but more regular M2. $4$     | 1 |

| 2.19 Coloring conflicts that may occur due to newly created tips 4            | 2 |

|                                                                               |   |

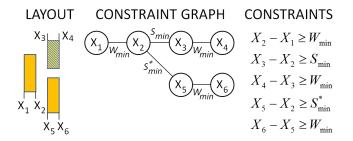

| 2.20 | Example of $x$ -direction constraint graph construction and constraint              |    |

|------|-------------------------------------------------------------------------------------|----|

|      | definition for a double-patterned layer. $W_{min}$ is the minimum width             |    |

|      | rule, $S_{min}$ is the S2S different-color spacing rule, and $S_{min}^*$ is the S2S |    |

|      | same-color spacing rule.                                                            | 49 |

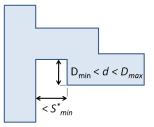

| 2.21 | Characteristics of notches that will be removed. $S_{min}^*$ is the side-to-        |    |

|      | side same-color spacing rule, $D_{min}$ is the notch-depth below which              |    |

|      | the notch is manufacturable with a single exposure, and $D_{\max}$ is the           |    |

|      | depth beyond which notch-filling is not performed to avoid creating                 |    |

|      | fat wires with larger spacing requirements.                                         | 51 |

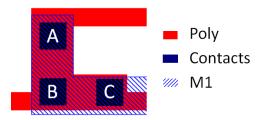

| 2.22 | Group of redundant contacts connecting to the Poly layer. Contact                   |    |

|      | B has more flexibility of movement than contacts A and C and, thus,                 |    |

|      | we pick B as the required contact and A and C as redundant contacts                 |    |

|      | that may be sacrificed if necessary to resolve conflicts                            | 52 |

| 2.23 | Illustration of M1 simplification for possible sacrifice of contacts                | 53 |

| 2.24 | Illustration of M1 simplification for possible sacrifice of pin segments.           | 53 |

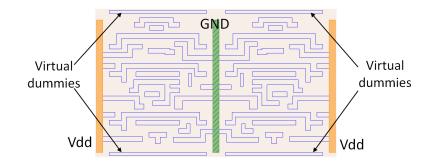

| 2.25 | Handling cell-boundary conflicts during placement (virtual dummies                  |    |

|      | not on mask)                                                                        | 55 |

| 2.26 | Violation count based on shape movement requirement: (a) layout                     |    |

|      | example with three spacing violations counted as two conflicts only                 |    |

|      | and (b) layout example with two spacing violations between the same                 |    |

|      | two polygons counted as two conflicts. The highlighted regions cor-                 |    |

|      | respond to possible issues with newly created tips at stitch locations              |    |

|      | (this will be discussed later)                                                      | 56 |

| 2.27 | Sample results for a cell layout: (a) before DP conflict removal, (b)               |    |

|      | after conflict removal with fixed area, and (c) after conflict removal              |    |

|      | with area increase.                                                                 | 58 |

|      |                                                                                     |    |

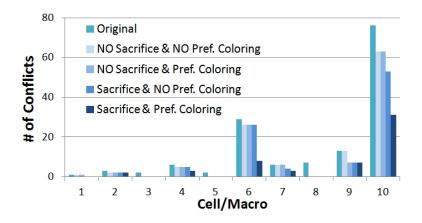

| 2.28 | Number of conflicts with the fixed-area flow for the different cell and                     |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | macro layouts showing the effects of using preferred coloring (see Fig-                     |    |

|      | ure 2.5) and the possible sacrifice of redundant contacts and M1 pin                        |    |

|      | segments.                                                                                   | 60 |

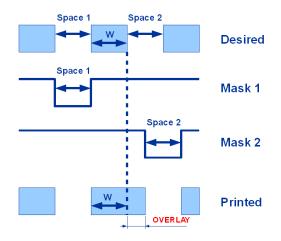

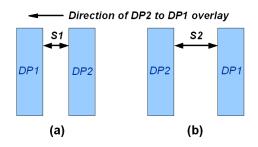

| 3.1  | Example layout with positive DP process (a) and negative DP process                         |    |

|      | (b) both using a positive-tone photoresist                                                  | 64 |

| 3.2  | Example showing translation of overlay error into CD variation in                           | 64 |

|      | negative DP                                                                                 | 64 |

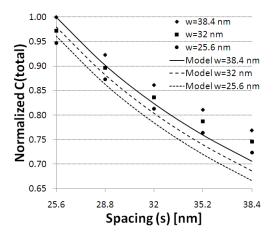

| 3.3  | Parallel plate capacitor model compared to simulation results for in-                       |    |

|      | terconnect capacitance with varying interconnect width and spacing.                         |    |

|      | Symbols represent simulated capacitances using Raphael <sup><math>TM</math></sup> [Rap] and |    |

|      | lines represent the capacitance evaluated using the parallel plate model.                   |    |

|      | Simulated and modeled capacitances are normalized with respect to                           |    |

|      | their maximum values                                                                        | 66 |

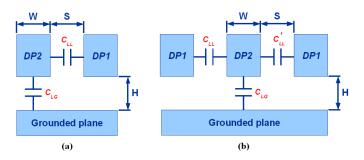

| 3.4  | Test structures used in the experiments: (a) 2-line structure, and (b)                      |    |

|      | 3-line structure with single grounded plane at the layer below                              | 69 |

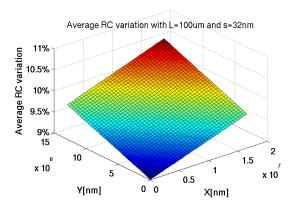

| 3.5  | Average $RC$ variation for the 2-line structure as a function of its                        |    |

|      | location in the design when overlay components are estimated                                | 72 |

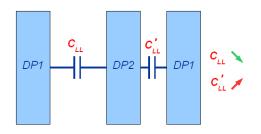

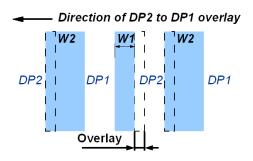

| 3.6  | Illustration of cancellation effect between line-to-line capacitances in                    |    |

|      | the 3-line structure                                                                        | 75 |

| 3.7  | Overlay impact dependence on layout decomposition in the 2-line                             |    |

|      | structure with positive DP: reduced spacing between lines for decom-                        |    |

|      | position of (a) and increased spacing between lines for decomposition                       |    |

|      | of (b)                                                                                      | 78 |

| 3.8  | Different overlay impact on wire width in negative DP                                       | 78 |

| 3.9  | Illustration of swizzled decomposition to reduce $\Delta RC$ of wires on                    |    |

|      | critical paths.                                                                             | 79 |

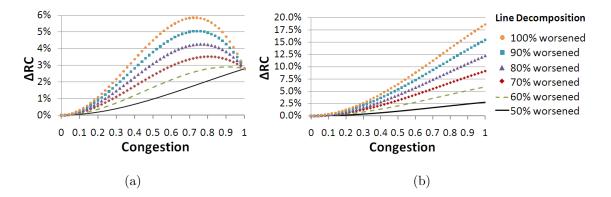

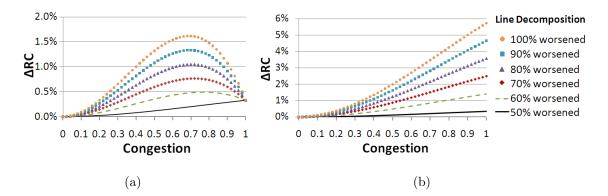

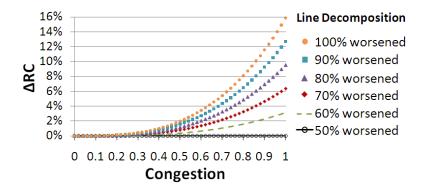

| 3.10 | Plot of path interconnect worst-case $\Delta RC$ versus congestion for differ-                                                           |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ent line splits between worsened and relieved $RC$ variation in positive                                                                 |    |

|      | DP process (a) and negative DP process (b). The plots assume an                                                                          |    |

|      | overlay budget equal to $20\%$ of half-pitch                                                                                             | 81 |

| 3.11 | Plot of path interconnect worst-case $\Delta RC$ versus congestion for differ-                                                           |    |

|      | ent line splits between worsened and relieved $RC$ variation in positive                                                                 |    |

|      | DP process (a) and negative DP process (b). The plots assume an                                                                          |    |

|      | overlay budget equal to $7\%$ of half-pitch                                                                                              | 81 |

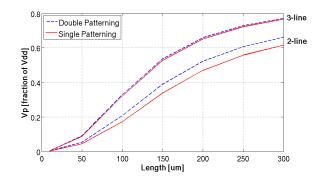

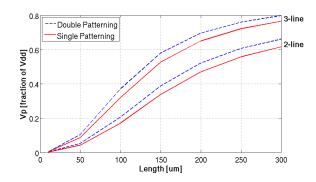

| 3.12 | Peak crosstalk noise versus interconnect length in positive DP process.                                                                  | 82 |

| 3.13 | Peak crosstalk noise versus interconnect length in negative DP process.                                                                  | 82 |

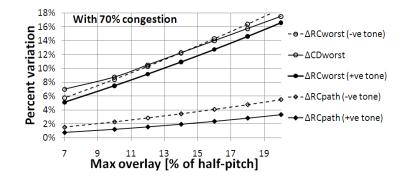

| 3.14 | Plots of average and worst case CD and $C$ variations versus require-                                                                    |    |

|      | ment of maximum overlay with $70\%$ congestion in positive and nega-                                                                     |    |

|      | tive DP                                                                                                                                  | 84 |

| 3.15 | Difference between worst-case interconnect $\Delta RC$ for a path in positive                                                            |    |

|      | process and negative process as a function of congestion for different                                                                   |    |

|      | line splits between worsened and relieved $RC$ variation                                                                                 | 85 |

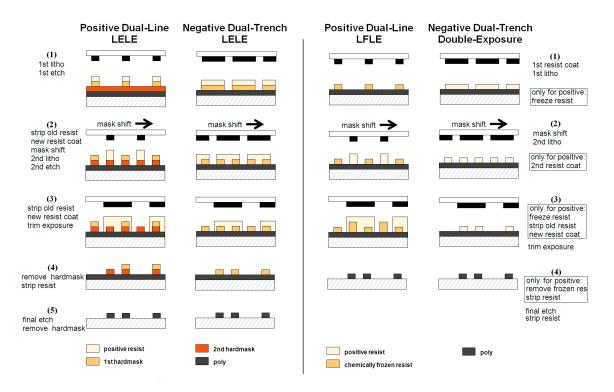

| 4.1  | Proposed manufacturing processes for STDP: positive dual-line and                                                                        |    |

|      | negative dual-trench LELE, positive dual-line LLE, a.k.a. litho-freeze-                                                                  |    |

|      | litho-etch (LFLE) process, and negative dual-trench double-exposure                                                                      |    |

|      | processes                                                                                                                                | 92 |

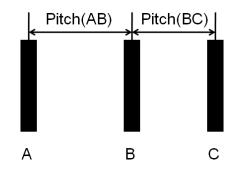

| 4.2  | Example illustrating gate-pitch restriction. In case $Pitch(AB)$ is                                                                      |    |

|      | $< X_0$ but different than X, then $Pitch(BC)$ must be either X or                                                                       |    |

|      | $\geq X_0$ and $Pitch(AC)$ must be $\geq X_0$ . Similarly, if $Pitch(BC)$ is un-                                                         |    |

|      | restricted, $Pitch(AB)$ is restricted to X or $\geq X_0$ and $Pitch(AC)$ to                                                              |    |

|      | $\geq X_0. \qquad \dots \qquad $ | 94 |

| 4.3  | Poly layer STDP critical mask snippet corresponding to a flip-flop                                                                       |    |

|      | cell with two structure-options (a) and (b)                                                                                              | 94 |

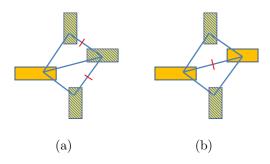

| 4.4  | Examples showing how the trim exposure resolves decomposition con-               |     |

|------|----------------------------------------------------------------------------------|-----|

|      | flicts                                                                           | 96  |

| 4.5  | Example of 4-input OAI cell layout migrated for the application of               |     |

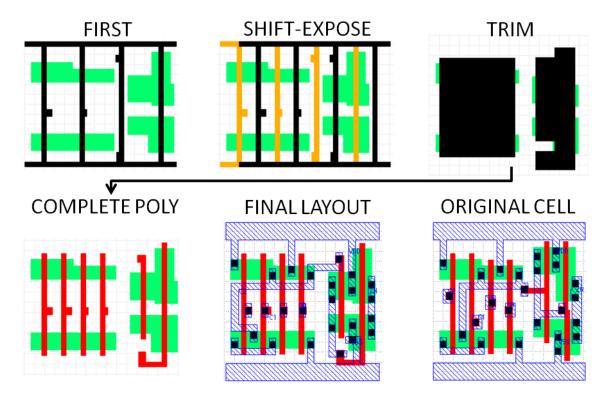

|      | STDP at the poly-line layer                                                      | 97  |

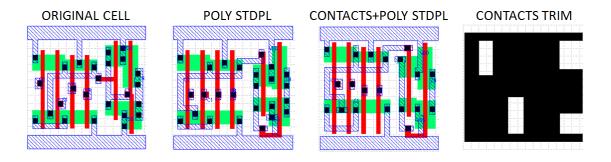

| 4.6  | Example of 4-input OAI cell layout migrated for the application of               |     |

|      | STDP at the poly and CA layers with 1.8× pitch relaxation                        | 98  |

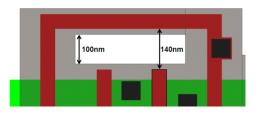

| 4.7  | Poly line-tip to poly side spacing rule of 140nm to ensure a minimum             |     |

|      | hole width of 100nm                                                              | 103 |

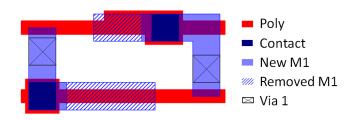

| 4.8  | Trim-mask complexity at cell-boundaries before (a) and after (b) en-             |     |

|      | forcing rules (2) and (3). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 103 |

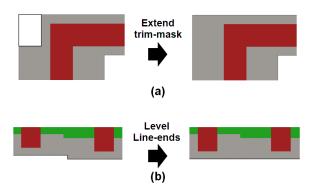

| 4.9  | Trim-mask notch-fill by (a) trim-mask extension and (b) poly line-end            |     |

|      | leveling                                                                         | 104 |

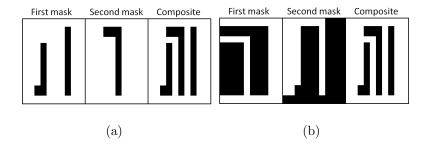

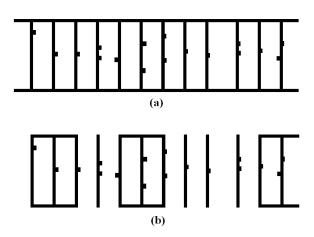

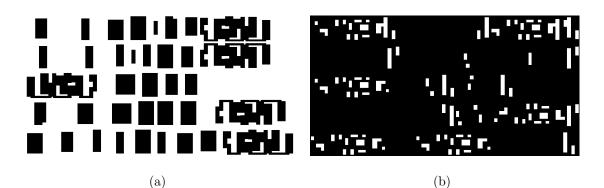

| 4.10 | Trim-mask layout snippet for poly-lines (a) and contacts (b). In (a),            |     |

|      | simple large blocks correspond to cells with unidirectional poly-lines           |     |

|      | and more complex shapes correspond to flip-flops with bidirectional              |     |

|      | poly-routing. In (b), both flip-flop and combinational logic regions             |     |

|      | have simple trim-mask features.                                                  | 105 |

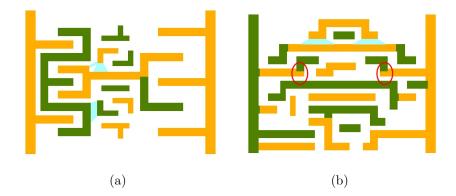

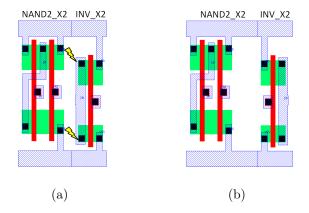

| 4.11 | Example of layout decomposition conflicts (marked with the arrows)               |     |

|      | between features of different cells (a) and our correct-by-construction          | 107 |

|      | cell layout that guarantees no conflicts (b)                                     | 107 |

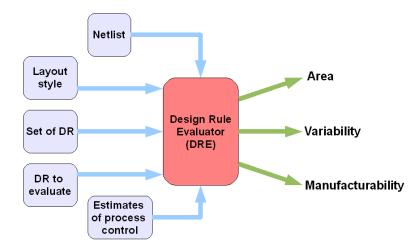

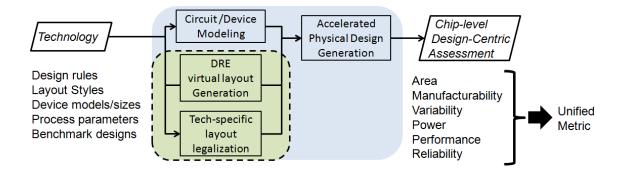

| 5.1  | Overview-diagram of DRE framework.                                               | 118 |

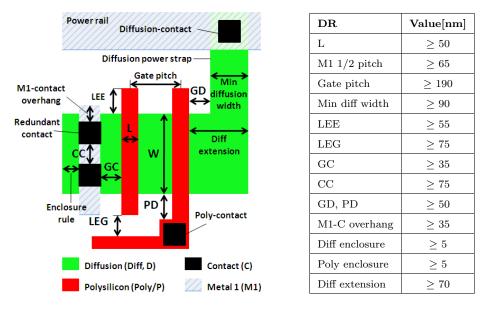

| 5.2  | Illustration of major DRs, their notations and values in FreePDK                 |     |

|      | 45nm process [Fre]                                                               | 119 |

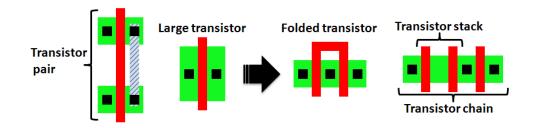

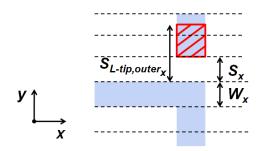

| 5.3  | Techniques and notations used in layout topology generation                      | 120 |

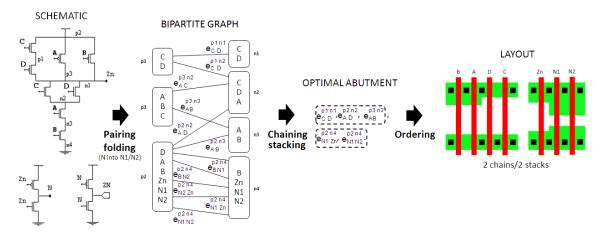

| 5.4  | Flow of layout topology generation in DRE framework                              | 121 |

| 5.5  | Example that illustrates our layout topology generation for a 4-input            |     |

|      | OAI standard-cell.                                                               | 122 |

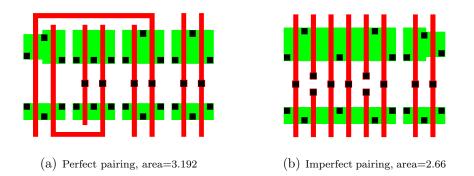

| 5.6  | Example illustrating imperfect pairing and its associated tradeoffs for                                        |

|------|----------------------------------------------------------------------------------------------------------------|

|      | a DLH_X2 cell layout                                                                                           |

| 5.7  | $\mathrm{S/D}\text{-}\mathrm{to}\text{-}\mathrm{gate}$ interconnections may be routed on M1 or poly layers and |

|      | $\rm S/D\text{-}to\text{-}S/D$ interconnections may be routed on M1 or M2 layers. We                           |

|      | assume a single-trunk Steiner tree for routing                                                                 |

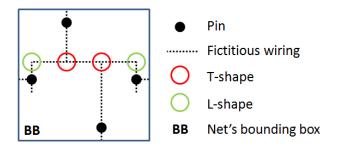

| 5.8  | Illustrating example showing how the shape count is determined for a                                           |

|      | 4-pin net based on the assumption of single-trunk Steiner tree routing. 128                                    |

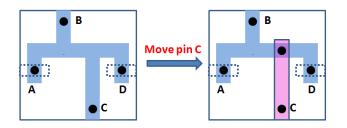

| 5.9  | Illustrating example showing the move of a pin from M1 to M2 to                                                |

|      | resolve congestion on M1                                                                                       |

| 5.10 | Overview of the algorithm used to determine the segments that need                                             |

|      | to be moved from M1 to M2 to resolve congestion on M1 129                                                      |

| 5.11 | Example illustrating blockage model for an instance of L-shape with                                            |

|      | a single tip facing its outer corner                                                                           |

| 5.12 | Overview of the algorithm used to determine blockage from rules that                                           |

|      | exceed the minimum spacing $(\sum Block_{x,y})$                                                                |

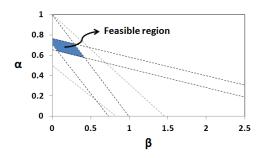

| 5.13 | Illustrating example for extraction of $\alpha$ and $\beta$ parameters of Equa-                                |

|      | tion 5.2 from M1 congestion data                                                                               |

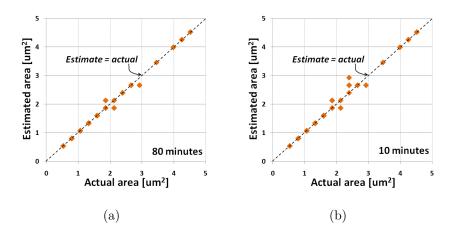

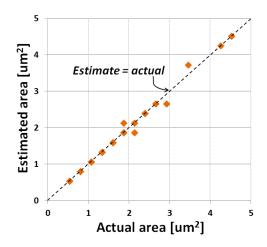

| 5.14 | DRE estimated cell area versus actual cell area of the Nangate Open                                            |

|      | Cell Library [Nana] (96 standard cells) with a runtime of 80 minutes                                           |

|      | and average absolute error less than $1\%$ (a) as well as a runtime of $10$                                    |

|      | minutes and average absolute error of $2\%$ (b)                                                                |

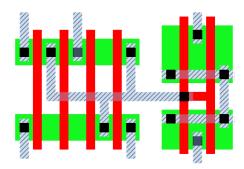

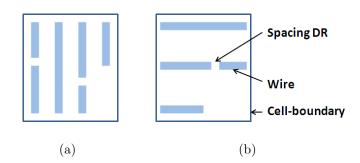

| 5.15 | Virtual artwork representation for (a) horizontal and (b) vertical M1                                          |

|      | wires                                                                                                          |

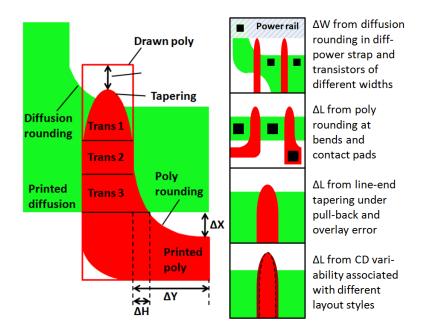

| 5.16 | Illustration of slicing model, rounding model parameters, and the                                              |

|      | sources of gate length and width variability considered in the DRE                                             |

|      | framework. Here, models for tapering and corner-rounding, rather                                               |

|      | than actual lithography simulation, are used to estimate the contours. $138$                                   |

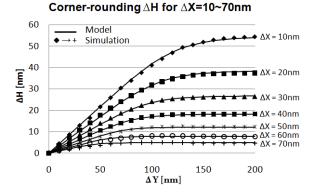

| 5.17 | Rounding model fitted to give $< 0.8 nm \; \Delta H$ error with measured data                    |   |

|------|--------------------------------------------------------------------------------------------------|---|

|      | from printed-image simulations on a fairly wide range of practical                               |   |

|      | corner-dimensions ( $\Delta X = 30 \rightarrow 70nm$ and $\Delta Y = 10 \rightarrow 200nm$ ) 139 | 9 |

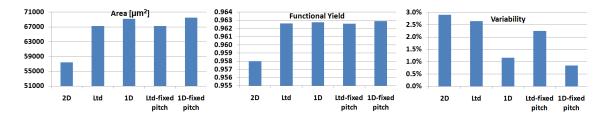

| 5.18 | Evaluation of restrictive poly-patterning styles on 45nm FreePDK                                 |   |

|      | $process^{13}$                                                                                   | 3 |

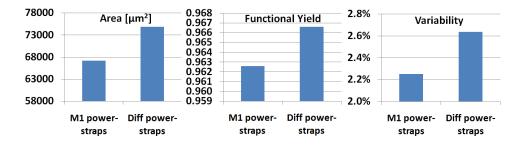

| 5.19 | Evaluation of M1/diffusion power-strap styles on $45$ nm FreePDK pro-                            |   |

|      | $cess^{13}$                                                                                      | 4 |

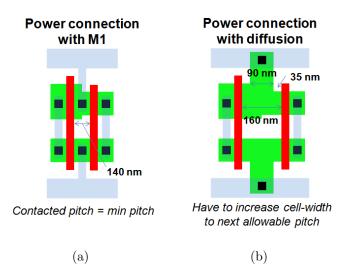

| 5.20 | Example of a layout with M1 power-strap (a) and with a diffusion                                 |   |

|      | power-strap (b)                                                                                  | 5 |

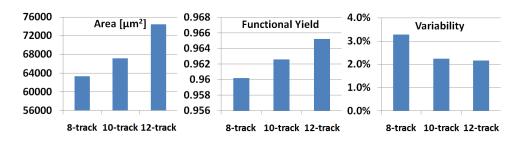

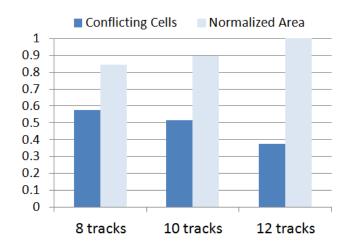

| 5.21 | Evaluation of $8/10/12$ -track cell height on 45nm FreePDK process <sup>13</sup> . 14            | 5 |

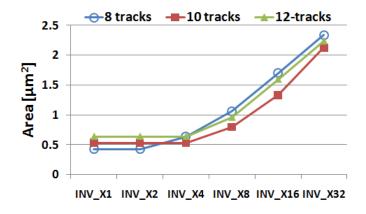

| 5.22 | Increasing area with increasing transistor width for $8/10/12$ -track cell                       |   |

|      | height                                                                                           | 6 |

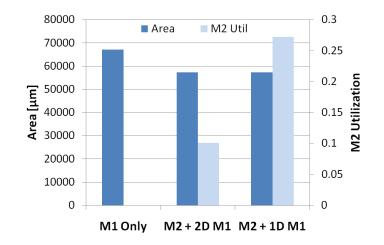

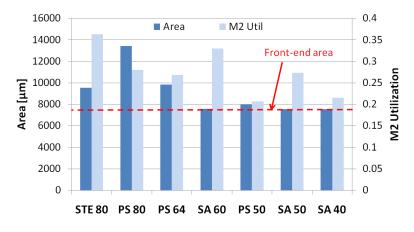

| 5.23 | Layout area and M2 utilization results when M2 is used only in case                              |   |

|      | of congestion on M1 and when M1 is unidirectional                                                | 7 |

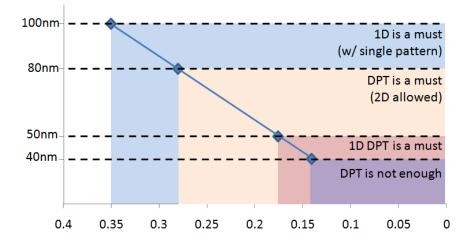

| 5.24 | Wiring pitch as a function of the $k_1$ factor and the limits of patterning                      |   |

|      | technologies and directionality (based on [Wal09])                                               | 8 |

| 5.25 | Examples of a PS-DPT forbidden patterns because of a coloring con-                               |   |

|      | flict (a) and a SADP forbidden pattern because a line-side that cannot                           |   |

|      | be defined except with the trim exposure $(b)^{16}$                                              | 0 |

| 5.26 | Layout area and M2 utilization results for STE, PS-DPT (PS), and                                 |   |

|      | SADP (SA) for M1/M2 pitch between 80 and 40nm. Front-end area                                    |   |

|      | denotes the area of diffusion, poly, and contacts layers                                         | 0 |

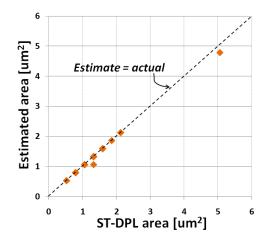

| 5.27 | DRE estimated cell area versus the actual area of ST-DPL compatible                              |   |

|      | cells designed manually (41 standard cells)                                                      | 1 |

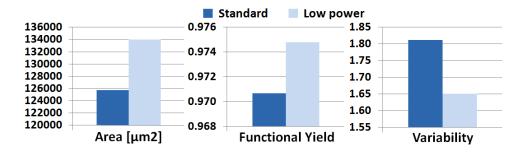

| 5.28 | Comparison between a standard and a low power 65nm process from                                  |   |

|      | the same commercial vendor                                                                       | 2 |

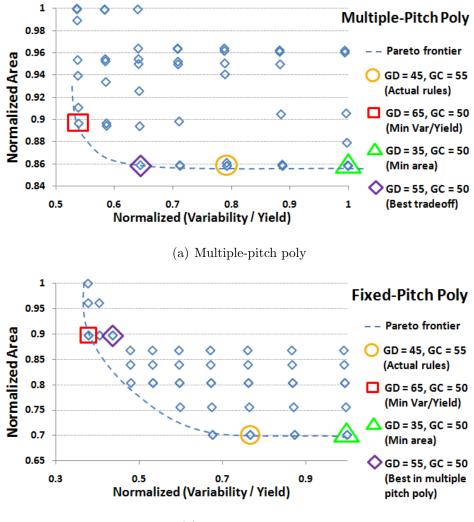

| 5.29 | Co-exploration of GC/GD rules (see figure 5.2) in a commercial $65\mathrm{nm}$                   |   |

|      | process with diffusion power-straps and limited routing                                          | 3 |

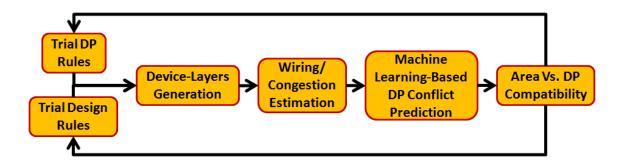

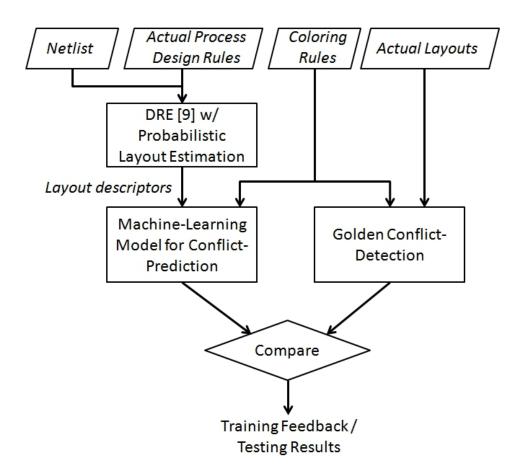

| 6.1  | Overview of our methodology for exploration of DP design rules 159             |  |

|------|--------------------------------------------------------------------------------|--|

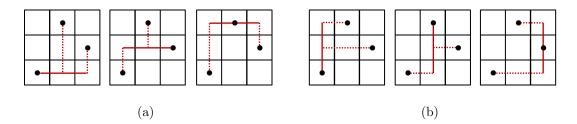

| 6.2  | Example of possible wiring solutions with single-trunk Steiner-tree            |  |

|      | topology for a three-pin net using (a) horizontal trunks and (b) ver-          |  |

|      | tical trunks                                                                   |  |

| 6.3  | Example of an unbalanced net and two of its possible solutions: (a) a          |  |

|      | typical horizontal trunk-based solution and (b) a pessimistic vertical         |  |

|      | trunk-based solution                                                           |  |

| 6.4  | Example of DR violation and associated extra track utilization 163 $$          |  |

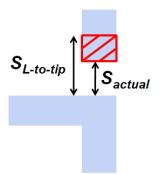

| 6.5  | Comparison of the estimated cell area of our approach with that of             |  |

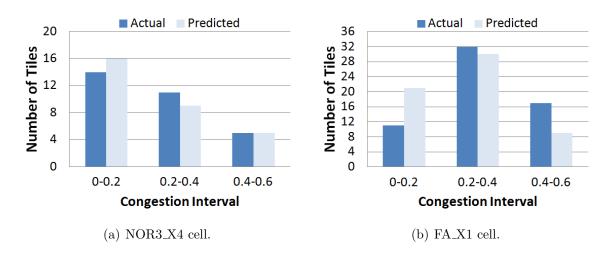

|      | actual cell-layouts using the same design rules                                |  |

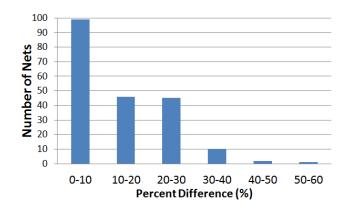

| 6.6  | Comparison between actual and predicted congestion                             |  |

| 6.7  | Percent difference between our wirelength estimates and that of FLUTE.166      |  |

| 6.8  | Overview of our machine learning based approach for conflict prediction. 167   |  |

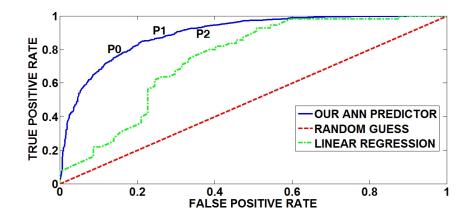

| 6.9  | ROC curve for our ANN model compared with those of linear regres-              |  |

|      | sion and random guess                                                          |  |

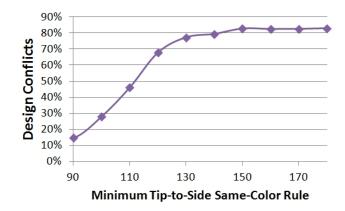

| 6.10 | Design Conflicts for range of tip-to-side same-color spacing rule 174          |  |

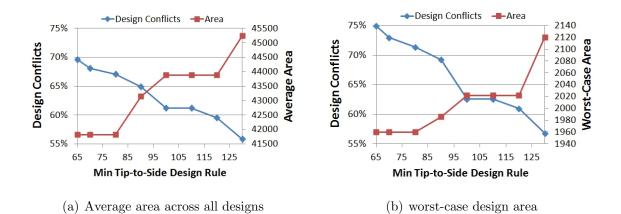

| 6.11 | Design Conflicts and area of benchmark designs for range of tip-to-            |  |

|      | side design rule                                                               |  |

| 6.12 | Design Conflicts and design area for 8-track, 10-track, and 12-track           |  |

|      | cell-heights                                                                   |  |

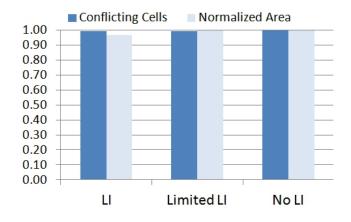

| 6.13 | Design Conflicts and design area by using: local interconnects $(LI)$ to       |  |

|      | perform poly-to-poly connections, LI to perform connections of only            |  |

|      | neighboring poly gates, and no LI                                              |  |

| 6.14 | Example of a DP-problematic layout pattern with an odd cycle in its            |  |

|      | conflict graph (a) that was broken by introducing a stitch (b) 178 $$          |  |

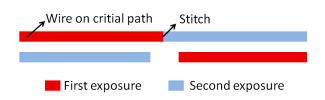

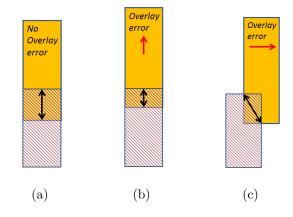

| 6.15 | Example of a stitch in a vertical line (a), a possible failure with overlay    |  |

|      | error in Y direction that may occur after line<br>end pullback (b), and a      |  |

|      | possible failure with overlay error in $X$ direction due to narrowing (c). 179 |  |

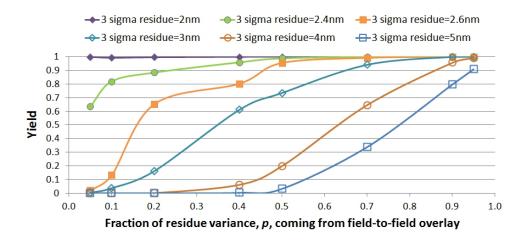

| 6.16 | 6 Plots showing the effects of the breakdown of overlay among field-to-       |  |

|------|-------------------------------------------------------------------------------|--|

|      | field and within-field overlay components for different overlay-residue       |  |

|      | values                                                                        |  |

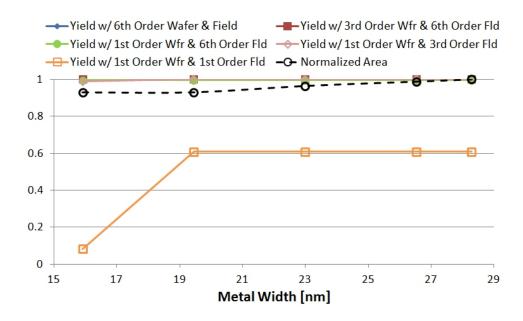

| 6.17 | Plots showing the interaction between the minimum line-width rule             |  |

|      | and overlay control and their impact on yield and layout area of the          |  |

|      | design with minimum overlap-length rule of 14nm                               |  |

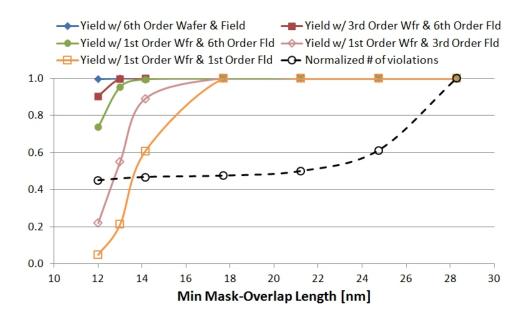

| 6.18 | Plots showing the interaction between the overlap-length rule and             |  |

|      | overlay control and their impact on yield and DP-compatibility of             |  |

|      | the design at the nominal line-width of 23nm                                  |  |

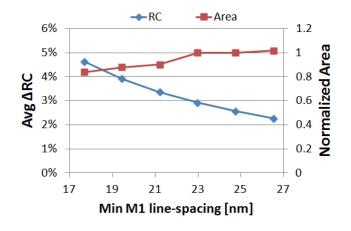

| 6.19 | Plot for the average $\Delta RC$ and the normalized design area for different |  |

|      | values of the minimum line-spacing rule                                       |  |

|      |                                                                               |  |

| 7.1  | Generalized design-centric assessor of technology                             |  |

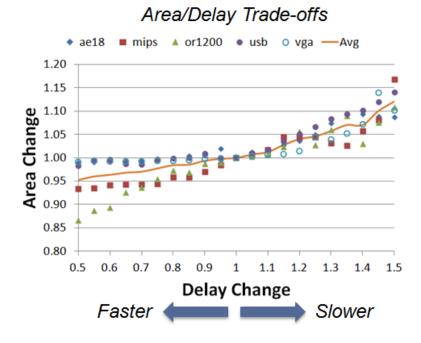

| 7.2  | Curves are generated based on purely-empirical experiments using              |  |

|      | existing synthesis/placement/routing tools                                    |  |

## LIST OF TABLES

| 2.1 | Results of our DP coloring at the M1 layer with two sets of same-                                                                                  |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | color spacing rules and comparison with our greedy and MINCUT-                                                                                     |    |

|     | based flipping approaches. The minimum different-color spacing rule                                                                                |    |

|     | is 65nm, while the minimum overlap length is 10nm                                                                                                  | 29 |

| 2.2 | Comparison of number of violations and stitches in a M2 layout col-                                                                                |    |

|     | ored with the pure ILP approach of [KPX10] and the same layout                                                                                     |    |

|     | colored with our greedy/MINCUT-based approaches                                                                                                    | 32 |

| 2.3 | Results of our DP coloring at the Poly and M2 layers (minimum-                                                                                     |    |

|     | spacing relaxation of 1.2× for Poly and 1.1× for M2) and compar-                                                                                   |    |

|     | ison with methods from previous work of [KPX10]. "Inst", "Viol",                                                                                   |    |

|     | "Secs", and "Stch" refer to number of instances, violations, user-time                                                                             |    |

|     | seconds, and stitches respectively, while "Min" refers to minimum                                                                                  |    |

|     | overlap length).                                                                                                                                   | 33 |

| 2.4 | Summary of results for the proposed TP coloring methodology when                                                                                   |    |

|     | applied on library and full-design layouts at $45$ , $32$ , $22$ , and $14$ nm nodes.                                                              | 40 |

| 2.5 | Results comparison between TP and DP coloring                                                                                                      | 42 |

| 2.6 | Summary of results for the proposed TP coloring methodology when                                                                                   |    |

|     | applied on library and full-design layouts at 45, 32, and 22nm nodes                                                                               |    |

|     | with pushed T2T and T2S same-color rules from 3X to 2X the mini-                                                                                   |    |

|     | mum spacing                                                                                                                                        | 43 |

| 2.7 | TP coloring results with and without employing the TP stitching                                                                                    |    |

|     | method (i.e., insertion of candidate stitches in S2S violating parts). $% \left( {{\left[ {{{\left[ {{\left[ {\left[ {{\left[ {{\left[ {{\left[ {$ | 44 |

| 2.8 | Run-time in real time of the proposed TP coloring methodology in-                                                                                  |    |

|     | cluding projection, graph constructions, and all 2-coloring steps (twelve                                                                          |    |

|     | steps).                                                                                                                                            | 44 |

| 2.9 | Results of applying our DP conflict removal method with and without<br>area increase to cells from a commercial 22nm library (area values are<br>normalized, "CF" stands for conflicts, "SRCA" stands for sacrificed |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | redundant contacts, and "Area Inc." stands for area increase)                                                                                                                                                        | 59  |

| 3.1 | Estimated overlay breakdown used in the reference experiment. $\ . \ .$                                                                                                                                              | 70  |

| 3.2 | Parameters and corresponding values used in the experiments                                                                                                                                                          | 71  |

| 3.3 | $\Delta RC$ results for the 2-line and 3-line structures in positive DP (in % form).                                                                                                                                 | 72  |

| 3.4 | $\Delta RC$ results for the 2-line and 3-line structures in negative DP (in % form).                                                                                                                                 | 73  |

| 3.5 | Average $\Delta RC$ across wafer for different values of wire length $(L)$ and spacing $(s)$ in case of the 2-line structure with positive DP                                                                        | 76  |

| 3.6 | Worst case $\Delta RC$ across wafer for different values of wire length $(L)$<br>and spacing $(s)$ in case of the 2-line structure with positive DP                                                                  | 76  |

| 3.7 | Average $\Delta RC$ across wafer for different values of wire length $(L)$ ,<br>width $(w)$ , and spacing $(s)$ in case of the 2-line structure with negative<br>DP                                                  | 77  |

| 3.8 | Worst case $\Delta RC$ across wafer for different values of wire length $(L)$ ,<br>width $(w)$ , and spacing $(s)$ in case of the 2-line structure with negative<br>DP                                               | 77  |

| 4.1 | Poly-line STDP compatible standard-cell library and associated area<br>with $1.8 \times$ pitch relaxation (area overhead is quantized because of<br>cell-pitch restrictions).                                        | 100 |

| 4.2 | Details of poly-line STDP compatible designs showing negligible area<br>overhead.                                                                                                                                    | 105 |

| 4.9 |                                                                                                                                                                                                                      | 100 |

| 4.3 | Details on trim-mask at the poly-line layer for the design of Table 4.2 showing very basic fabrication requirements.                                                                                                 | 106 |

| 4.4 | Poly-line plus CA STDP compatible standard-cell library and associ-           |

|-----|-------------------------------------------------------------------------------|

|     | ated area (in $[um^2])$ with $1.8\times$ pitch relaxation. Note that the area |

|     | overhead is quantized due to cell-pitch restrictions from place and           |

|     | route. O/H stands for overhead                                                |

| 4.5 | Cell-area (in $[um^2])$ of three designs synthesized using Poly plus CA       |

|     | STDP compatible cells for the different schemes. O/H stands for               |

|     | overhead                                                                      |

| 4.6 | Details on trim-mask at the contacts layer for the design of Table $4.2$      |

|     | showing very basic fabrication requirements                                   |

| 4.7 | Summary of STDP overlay benefits                                              |

| 4.8 | Summary of comparison between standard-DP and STDP methods 113                |

|     |                                                                               |

| 5.1 | Shape count and locations assumptions for nets that cannot be con-            |

|     | nected with a straight line                                                   |

| 5.2 | Parameter definition for equation 5.1                                         |

| 5.3 | Spacing rules considered in the DRE framework for both $x$ and $y$            |

|     | directions                                                                    |

| 5.4 | BENCHMARK DESIGNS USED IN OUR EXPERIMENTS AND THEIR CORRESPONDING             |

|     | Number of cell instances and unique cell types                                |

| 5.5 | process control parameters used in our experiments                            |

| 5.6 | Summary of patterning styles and rules assumptions made for each              |

|     | technology in our study                                                       |

| 6.1 | Spacing rules in vertical and horizontal directions considered in our         |

| 0.1 | framework of rule violations impact on wiring congestion                      |

| 6.2 |                                                                               |

|     |                                                                               |

| 6.3 | Summary of the Properties of the ANN Model                                    |

| 6.4 | Results of testing the ANN model on cell layouts                              |

| 6.5 | BENCHMARK DESIGNS USED IN OUR EXPERIMENTS AND THEIR CORRESPONDING |     |

|-----|-------------------------------------------------------------------|-----|

|     | NUMBER OF CELL INSTANCES AND UNIQUE CELL TYPES                    | 173 |

#### Acknowledgments

I would like to dedicate this dissertation to my family. To Said, my father, my inspiration and role model of perseverance and willpower. He showed me that no matter how big the dream is, I will achieve it with "enough" determination. I only wish I could take a leaf out of his book. To Nabila, my mother, my *"let it be"* symbol and the source of my creativity. She showed me that no matter how complicated the situation gets, I can always find a way to make things right. To my siblings, Houssam, Rania, and Hikmat, my lifelong best friends and my strength pillar. They were always there to support me and give me much needed advice. I cordially thank all my family, including Hayat, Sara and Zeina, for the endless love and caring they have given me.

I would like to take this opportunity to express my gratitude to my mentors and teachers.

To Prof. Puneet Gupta, my academic advisor and guide throughout my PhD studies. He showed me the way to approach research and helped me develop many of my research skills. His teachings, encouragement, and counseling, were most crucial to my achievement.

To Dr. Lars Liebmann, my mentor during my second internship at IBM and my role model of what an engineer and scientist should be. He was a source of inspiration and enlightenment. The many research discussions I had with Lars resulted in many original ideas, much of which I have incorporated into my research work.

To Dr. Kanak Agarwal, my mentor during my first internship at IBM. Kanak was always ready to discuss research and exposed me to many research ideas which resulted in a considerable part of this work. He also helped me find and convey the value of my ideas.

To Dr. Sani Nassif, my manager during my first internship at IBM. His visionary aptitude inspired me to look at research from a broader angle. I would also like to thank him for giving me the opportunity to start a great chapter in my career working with the many exceptional researchers at IBM.

I would like to sincerely thank my committee members, Prof. Jason Cong, Prof. Lei He, and Prof. Dejan Markovic, for their valuable feedback on my research and their enlightening teachings.

It is a pleasure to express my thanks to my friends and colleagues at NanoCAD lab of UCLA for the good times we spent together and for the help they have given me in my research work.