#### UNIVERSITY OF CALIFORNIA

Los Angeles

Efficient Machine Learning

Acceleration at the Edge

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Wojciech Piotr Romaszkan

© Copyright by Wojciech Piotr Romaszkan 2023

#### ABSTRACT OF THE DISSERTATION

Efficient Machine Learning

Acceleration at the Edge

by

Wojciech Piotr Romaszkan

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2023

Professor Puneet Gupta, Chair

My thesis is a result of a confluence of several trends that have emerged in recent years. First, the rapid proliferation of deep learning across the application and hardware landscapes is creating an immense demand for computing power. Second, the waning of Moore's Law is paving the way for domain-specific acceleration as a means of delivering performance improvements. Third, deep learning's inherent error tolerance is reviving long-forgotten approximate computing paradigms. Fourth, latency, energy, and privacy considerations are increasingly pushing deep learning towards edge inference, with its stringent deployment constraints. All of the above have created a unique, once-in-a-generation opportunity for accelerated widespread adoption of new classes of hardware and algorithms, provided they can deliver fast, efficient, and accurate deep learning inference within a tight area and energy envelope.

One approach towards efficient machine learning acceleration that I have explored attempts to push a neural network model size to its absolute minimum. 3PXNet - Pruned, Permuted, Packed XNOR Networks combines two widely used model compression techniques:

binarization and sparsity to deliver usable models with a size down to single kilobytes. It uses an innovative combination of weight permutation and packing to create structured sparsity that can be implemented efficiently in both software and hardware. 3PXNet has been deployed as an open-source library targeting microcontroller-class devices with various software optimizations, further improving runtime and storage requirements.

The second line of work I have pursued is the application of stochastic computing (SC). It is an approximate, stream-based computing paradigm enabling extremely area-efficient implementations of basic arithmetic operations such as multiplication and addition. SC has been enjoying a renaissance over the past few years due to its unique synergy with deep learning. On the one hand, SC makes it possible to implement extremely dense multiply-accumulate (MAC) computational fabric well suited towards computing large linear algebra kernels, which are the bread-and-butter of deep neural networks. On the other hand, those neural networks exhibit immense approximation tolerance levels, making SC a viable implementation candidate.

However, several issues need to be solved to make the SC acceleration of neural networks feasible. The area efficiency comes at the cost of long stream processing latency. The conversion cost between fixed-point and stochastic representations can cancel out the gains from computation efficiency if not managed correctly. The above issues lead to a question on how to design an accelerator architecture that best takes advantage of SC's benefits and minimizes its shortcomings. To address this, I proposed the ACOUSTIC (Accelerating Convolutional Neural Networks through Or-Unipolar Skipped Stochastic Computing) architecture and its extension - GEO (Generation and Execution Optimized Stochastic Computing Accelerator for Neural Networks). ACOUSTIC is an architecture that tries to maximize SC's compute density to amortize conversion costs and memory accesses, delivering system-level reduction in inference energy and latency. It has taped out and demonstrated in silicon, using a 14nm fabrication process. GEO addresses some of the shortcomings of ACOUSTIC. Through the introduction of near-memory computation fabric, GEO enables a more flexible selection of

dataflows. Novel progressive buffering scheme unique to SC lowers the reliance on high memory bandwidth. Overall, my work tries to approach accelerator design from the systems perspective, making it stand apart from most recent SC publications targeting point improvements in the computation itself.

As an extension to the above line of work, I have explored the combination of SC and sparsity, to apply it to new classes of applications, and enable further benefits. I have proposed the first SC accelerator that supports weight sparsity - SASCHA (Sparsity-Aware Stochastic Computing Hardware Architecture for Neural Network Acceleration), which can improve performance on pruned neural networks, while maintaining the throughput when processing dense ones. SASCHA solves a series of unique, non-trivial challenges of combining SC with sparsity. On the other hand, I have also designed an architecture for accelerating event-based camera object tracking - SCIMITAR. Event-based cameras are relatively new imaging devices which only transmit information about pixels that have changed in brightness, resulting in very high input sparsity. SCIMITAR combines SC with computing-in-memory (CIM), and, through a series of architectural optimizations, is able to take advantage of this new data format to deliver low-latency object detection for tracking applications.

The dissertation of Wojciech Piotr Romaszkan is approved.

Mani B. Srivastava

Sudhakar Pamarti

Anthony J. Nowatzki

Puneet Gupta, Committee Chair

University of California, Los Angeles 2023 To Camila.

# TABLE OF CONTENTS

| 1 | Intr | roducti | ion                                                            | 1  |

|---|------|---------|----------------------------------------------------------------|----|

|   | 1.1  | Model   | l Compression: Better, Faster, Smaller                         | 2  |

|   |      | 1.1.1   | Fewer Bits - Quantization & Binarization                       | 2  |

|   |      | 1.1.2   | Alternate Number Representations                               | 3  |

|   |      | 1.1.3   | Fewer Values - Sparsity & Pruning                              | 4  |

|   |      | 1.1.4   | Edge Models & Libraries                                        | 6  |

|   | 1.2  | Stocha  | astic Computing - Processing with Random Streams               | 6  |

|   |      | 1.2.1   | Number Representation                                          | 7  |

|   |      | 1.2.2   | Multiplication and Accumulation                                | 8  |

|   |      | 1.2.3   | Stochastic Neural Network Functions                            | 10 |

|   | 1.3  | Doma    | in-Specific Acceleration - Breaking the Shackles of Generality | 11 |

|   | 1.4  | Disser  | tation Outline                                                 | 12 |

| 2 | 3РУ  | KNet -  | Fewer Bits, More Zeros                                         | 14 |

|   | 2.1  | A Cas   | se for Sparse XNOR Networks                                    | 15 |

|   | 2.2  | The 3   | PXNet Approach                                                 | 17 |

|   |      | 2.2.1   | Challenges in pruning XNOR networks                            | 17 |

|   |      | 2.2.2   | Pruning a packed XNOR network                                  | 19 |

|   |      | 2.2.3   | Training 3PXNets                                               | 21 |

|   | 2.3  | Imple   | menting 3PXNet                                                 | 24 |

|   |      | 2.3.1   | Fully-Connected Layers                                         | 25 |

|   |      | 2.3.2   | Convolutional Layers                                           | 28 |

|   |     | 2.3.3  | Fused kernels                                         | 32 |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | 2.3.4  | ARM NEON Support                                      | 33 |

|   |     | 2.3.5  | Binarization of the First Layer                       | 34 |

|   | 2.4 | Exper  | imental Setup                                         | 34 |

|   |     | 2.4.1  | Platforms                                             | 35 |

|   |     | 2.4.2  | Benchmarks                                            | 35 |

|   |     | 2.4.3  | Baseline                                              | 36 |

|   | 2.5 | Result | s and Discussion                                      | 36 |

|   |     | 2.5.1  | Accuracy & Model Size                                 | 36 |

|   |     | 2.5.2  | Performance & Energy                                  | 39 |

|   | 2.6 | Distin | ction between 3PXNet and Ternary Networks             | 42 |

|   | 2.7 | Conclu | usion                                                 | 42 |

| 3 | AC  | OUST   | IC - Accelerator Built on Randomness                  | 44 |

|   | 3.1 | Introd | $egin{array}{cccccccccccccccccccccccccccccccccccc$    | 45 |

|   | 3.2 | ACOU   | JSTIC Optimizations for DNNs                          | 48 |

|   |     | 3.2.1  | Split-Unipolar Representation                         | 48 |

|   |     | 3.2.2  | OR-based Scaling-Free Accumulation                    | 49 |

|   |     | 3.2.3  | Computation Skipping using Stochastic Average Pooling | 51 |

|   | 3.3 | ACOU   | JSTIC Architecture                                    | 51 |

|   |     | 3.3.1  | Understanding SC Benefits                             | 52 |

|   |     | 3.3.2  | Accelerator Architecture                              | 55 |

|   |     | 3.3.3  | Control                                               | 65 |

|   |     | 3.3.4  | Evaluated ACOUSTIC Architectures                      | 67 |

|   | 3.4 | Evalua | ation & Results                                     |

|---|-----|--------|-----------------------------------------------------|

|   |     | 3.4.1  | Evaluation Methodology                              |

|   |     | 3.4.2  | ACOUSTIC Accuracy                                   |

|   |     | 3.4.3  | Runtime Configurable Precision                      |

|   |     | 3.4.4  | Area & Power Breakdown                              |

|   |     | 3.4.5  | Performance Comparisons                             |

|   | 3.5 | FPGA   | Evaluation                                          |

|   | 3.6 | Demo   | nstration Chip                                      |

|   |     | 3.6.1  | Architecture                                        |

|   |     | 3.6.2  | SC Computation                                      |

|   |     | 3.6.3  | Computation Mapping                                 |

|   |     | 3.6.4  | Evaluation & Results                                |

|   | 3.7 | Relate | ed Work                                             |

|   |     | 3.7.1  | Deep Learning using Stochastic Computing            |

|   |     | 3.7.2  | Approximate and Programmable Precision Accelerators |

|   | 3.8 | Conclu | asion                                               |

| 4 | GE  | 0 - Pu | shing Stochastic Computing Further                  |

|   | 4.1 | Introd | uction                                              |

|   | 4.2 | Stocha | astic Stream Generation Optimizations               |

|   |     | 4.2.1  | Co-optimized Shared Generation and Training         |

|   |     | 4.2.2  | Progressive Stochastic Stream Generation            |

|   | 4.3 | Stocha | astic Computing Execution Optimizations             |

|   |     | 4.3.1  | GEO Architecture                                    |

|   |     | 4.3.2  | Partial Binary Accumulation            |

|---|-----|--------|----------------------------------------|

|   |     | 4.3.3  | Near-Memory Computation                |

|   |     | 4.3.4  | Pipeline Optimizations                 |

|   | 4.4 | Evalua | ation & Results                        |

|   |     | 4.4.1  | Evaluation Methodology                 |

|   |     | 4.4.2  | GEO Accuracy Comparisons               |

|   |     | 4.4.3  | Performance Impact of GEO Enhancements |

|   |     | 4.4.4  | GEO Performance Compared               |

|   | 4.5 | Concl  | usion                                  |

| 5 | SAS | SCHA   | - Combining Randomness with Sparsity   |

|   | 5.1 | Introd | luction                                |

|   | 5.2 | Motiv  | ation                                  |

|   | 5.3 | SASC   | HA Sparse SC PE                        |

|   |     | 5.3.1  | Sparse PE Design Objectives            |

|   |     | 5.3.2  | G:C Sparse PE                          |

|   |     | 5.3.3  | Multi-Group Sparse SC PE               |

|   |     | 5.3.4  | SASCHA PE Analytical Model             |

|   |     | 5.3.5  | Parallel Stream Processing             |

|   | 5.4 | SASC   | HA Architecture                        |

|   |     | 5.4.1  | SASCHA Accelerator                     |

|   |     | 5.4.2  | SASCHA Asynchronous Scheduler          |

|   |     | 5.4.3  | Memory Organization                    |

|   | 5.5 | Bit_Sl | icing Weights                          |

|   | 5.6 | Evalua | ation & Results                                              |

|---|-----|--------|--------------------------------------------------------------|

|   |     | 5.6.1  | SASCHA Accuracy                                              |

|   |     | 5.6.2  | Performance Results                                          |

|   | 5.7 | Relate | ed Work                                                      |

|   |     | 5.7.1  | Sparse Accelerators                                          |

|   |     | 5.7.2  | Stochastic Computing Accelerators                            |

|   | 5.8 | Concl  | usion                                                        |

| 6 | SCI | MITA   | R: Event-Based Tracking with Stochastic Compute-In-Memory149 |

|   | 6.1 | Introd | luction                                                      |

|   | 6.2 | Motiv  | ation                                                        |

|   |     | 6.2.1  | Event-Based Cameras                                          |

|   |     | 6.2.2  | Event-Based Data Processing                                  |

|   |     | 6.2.3  | Stochastic Computing In-Memory                               |

|   | 6.3 | SCIM   | ITAR Implementation                                          |

|   |     | 6.3.1  | Stochastic Compute-in-Memory Macro with In-Situ SNG 161      |

|   |     | 6.3.2  | In-Situ Stochastic Number Generator                          |

|   |     | 6.3.3  | In-Memory Stochastic MAC Unit                                |

|   |     | 6.3.4  | Event-Based SCIM Accelerator Architecture                    |

|   |     | 6.3.5  | Multi-Level Early Termination                                |

|   | 6.4 | Evalua | ation                                                        |

|   |     | 6.4.1  | Accuracy                                                     |

|   |     | 6.4.2  | Hardware Evaluation                                          |

|   | 6.5 | Concl  | usion                                                        |

| 7 | Con   | clusio | n                                                |

|---|-------|--------|--------------------------------------------------|

|   | 7.1   | Overv  | iew of Contributions                             |

|   |       | 7.1.1  | 3PXNet                                           |

|   |       | 7.1.2  | ACOUSTIC & GEO                                   |

|   |       | 7.1.3  | SASCHA                                           |

|   |       | 7.1.4  | SCIMITAR                                         |

|   | 7.2   | Direct | ions for Future Work                             |

|   |       | 7.2.1  | Exploration of Stochastic Computing Accelerators |

|   |       | 7.2.2  | Analog Stochastic Computing                      |

|   |       | 7.2.3  | Extending 3PXNet                                 |

| R | efere | nces   |                                                  |

### LIST OF FIGURES

| 1.1  | Stochastic Number Generator Circuit (SNG) with an AND gate SC multipli-                                                                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | cation (c)                                                                                                                                                        | 7  |

| 1.2  | RMS error of the bit stream representation for a given value a), and area $[\mu m^2]$ comparison between different SC MACs, depending on the number of inputs b). | 9  |

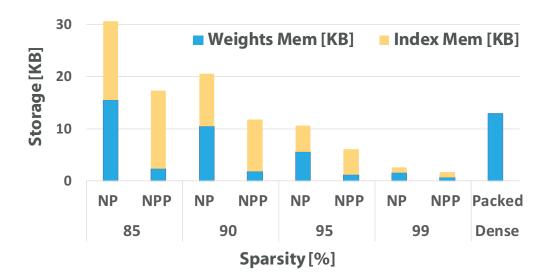

| 2.1  | Storage requirements for Dense, NP and NPP XNOR "small" MNIST MLP for varying levels of sparsity                                                                  | 19 |

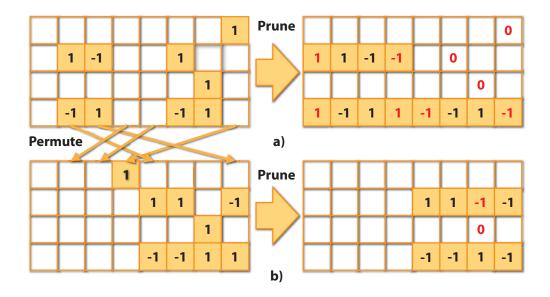

| 2.2  | Pruning with packing constraint of 4 bits a) without permutation, b) with permutation                                                                             | 21 |

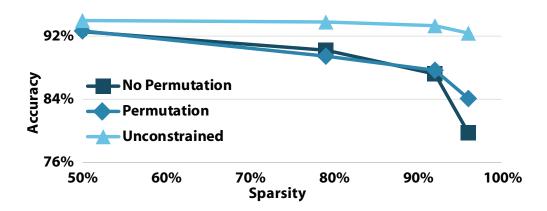

| 2.3  | Comparison of training results with and without permutation for different sparsities.                                                                             | 22 |

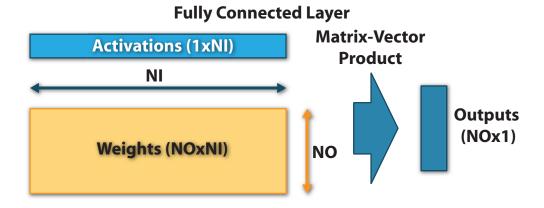

| 2.4  | A schematic view of a fully-connected layer with NI inputs and NO kernels                                                                                         | 24 |

| 2.5  | A schematic view of a padded convolutional layer followed by pooling operation.                                                                                   | 25 |

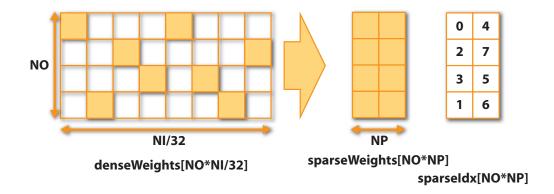

| 2.6  | 256x4 fully-connected layer weight and index storage with $75%$ sparsity (NP= $2x$                                                                                |    |

|      | 32-bit packs per output)                                                                                                                                          | 28 |

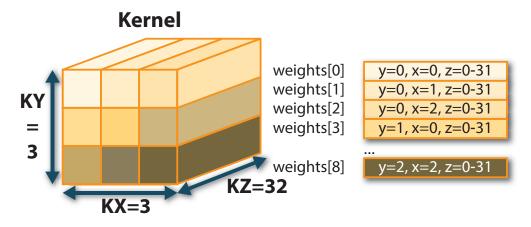

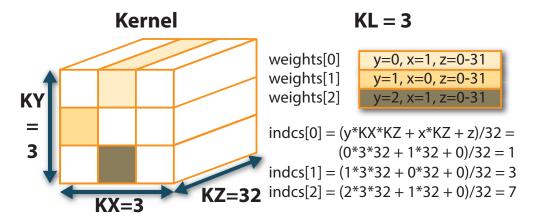

| 2.7  | 3x3x32 kernel packed into depth-first binarized vectors                                                                                                           | 29 |

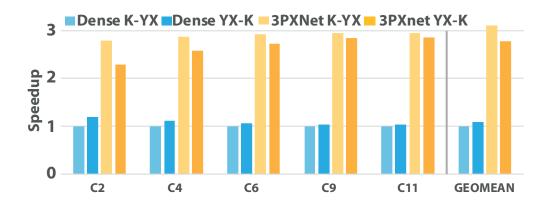

| 2.8  | Dense and 3PXNet (93.75% sparsity) speedups for kernel as an outer (K-YX) and inner (YX-K) loop for different VGG-16D [1] layers, normalized to dense K-YX.       | 30 |

| 2.9  | 3x3x32 Convolution kernel weight packs and indices with KL=3 active packs                                                                                         | 31 |

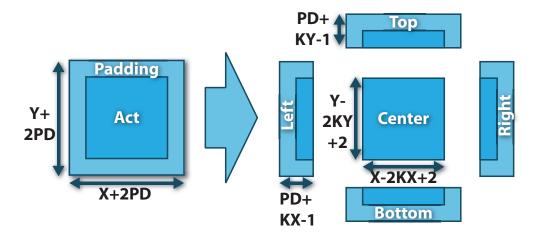

| 2.10 | Convolution splitting into padded and non-padded regions for efficient computa-                                                                                   |    |

|      | tion                                                                                                                                                              | 33 |

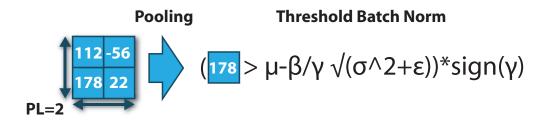

| 2.11 | A 2x2 fused Max Pooling followed by threshold Batch Normalization                                                                                                 | 34 |

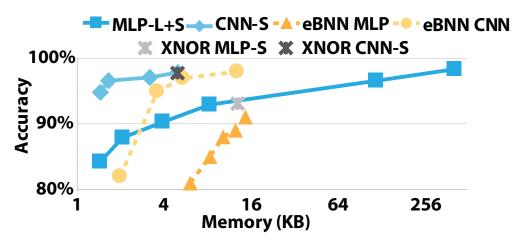

| 2.12 | Accuracy vs. Memory tradeoff compared to eBNN and dense XNOR                                                                                                      | 37 |

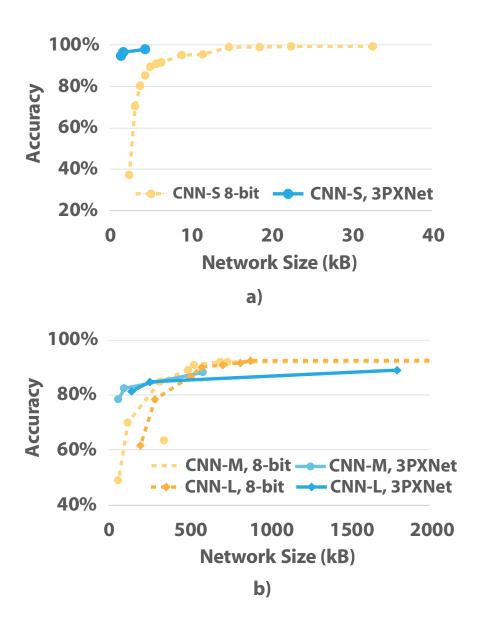

| 2.13 | Accuracy comparison between sparse 8-bit network and 3PXNet, for MNIST (a)          |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | and CIFAR-10 (b)                                                                    | 40  |

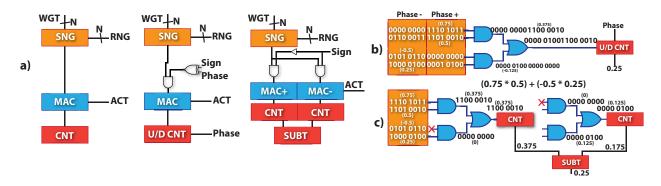

| 3.1  | Circuit level support for unipolar, temporal split-unipolar, and spatial split-     |     |

|      | unipolar representations (a) and an example of 2-wide split-unipolar MAC temporaril | ly- |

|      | (b) and spatially-unrolled c)                                                       | 49  |

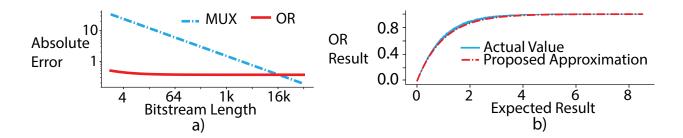

| 3.2  | Accuracy comparison between MUX and OR a) and comparison of approximation           |     |

|      | methods for OR accumulation b)                                                      | 50  |

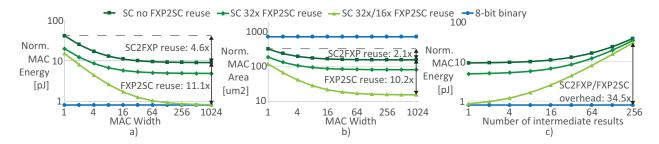

| 3.3  | Normalized MAC energy (a) and area (b) for 8-bit fixed-point and 256-long,          |     |

|      | unipolar SC implementations in TSMC 28nm node with 200MHz clock, with               |     |

|      | different data reuse patterns. Normalized MAC energy for 256-wide MAC when          |     |

|      | intermediate results are converted to binary (c)                                    | 53  |

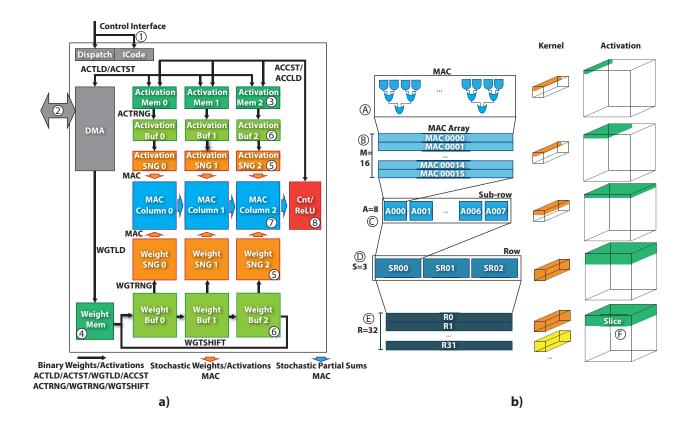

| 3.4  | Block diagram of the proposed ACOUSTIC accelerator (a), and the hierarchical        |     |

|      | organization of the compute engine with parts of the kernel and activation tensors  |     |

|      | covered by each level of hierarchy (b)                                              | 56  |

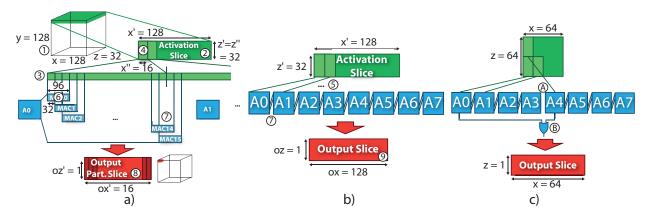

| 3.5  | Convolving a $1x128x32$ input slice with a $1x3x32$ kernel to compute a $1x16x1$    |     |

|      | partial output slice a). Extension across multiple arrays to compute a 1x128x1      |     |

|      | output slice b). Configuration for a 1x64x64 input tensor                           | 59  |

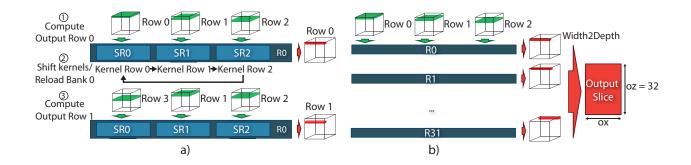

| 3.6  | Processing two successive output rows sequentially (a), processing multiple ker-    |     |

|      | nels at the same time, with output transposition (b)                                | 61  |

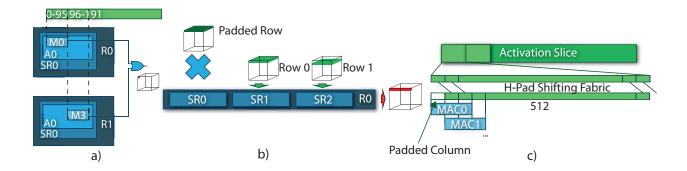

| 3.7  | Extending kernel size up to 6x6 by coupling adjacent rows (a), enabling padding     |     |

|      | through row scheduling for height (b) and configurable shifting fabric before array |     |

|      | inputs for width (c)                                                                | 62  |

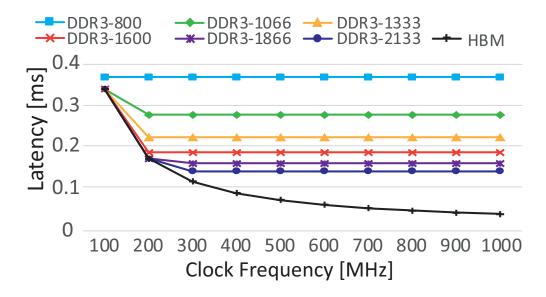

| 3.8  | Latency of processing a convolutional layer with 16x16x512 inputs and 512 3x3x512     |    |

|------|---------------------------------------------------------------------------------------|----|

|      | kernels and pre-loading 512 $3x3x512$ kernels for the subsequent layers using differ- |    |

|      | ent clock frequency and external memory interfaces, using temporarily-unrolled        |    |

|      | 256-long split-unipolar streams                                                       | 68 |

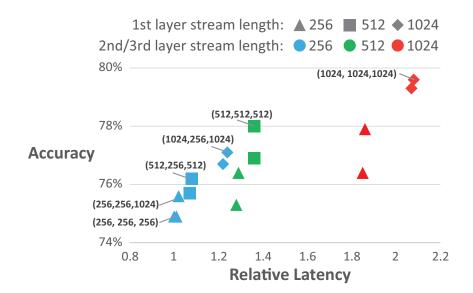

| 3.9  | Accuracy and performance at different stream lengths for the CIFAR-10 CNN on          |    |

|      | ACOUSTIC ULP. Labeled points are pareto points with the numbers representing          |    |

|      | stream lengths in 1st layer, 2nd & 3rd layer, and 4th layer                           | 72 |

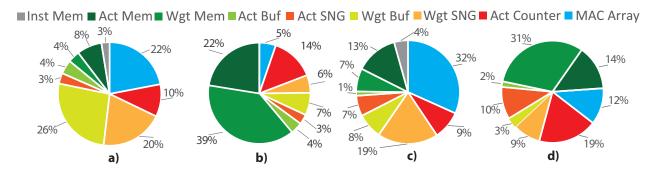

| 3.10 | Area breakdown for ACOUSTIC LP (a) and ULP (b) and power breakdown for                |    |

|      | ACOUSTIC LP (c) and ULP (d)                                                           | 72 |

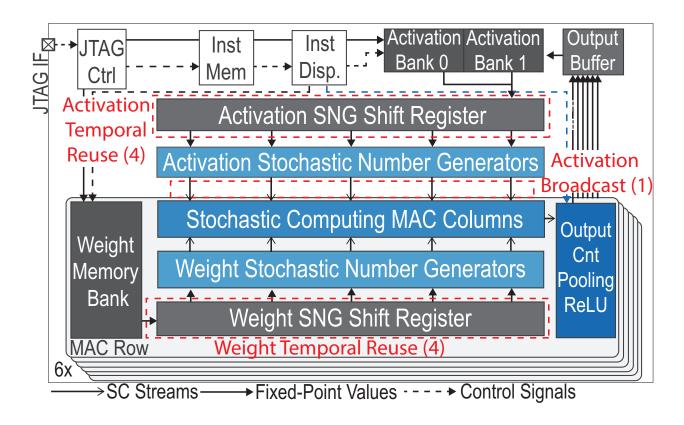

| 3.11 | Overall accelerator architecture                                                      | 78 |

| 3.12 | SC split-unipolar MAC and stochastic average pooling (top). Precision-latency         |    |

|      | trade-off using different stream lengths (bottom)                                     | 79 |

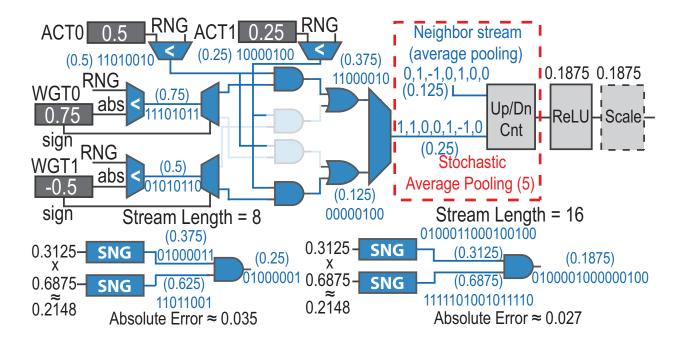

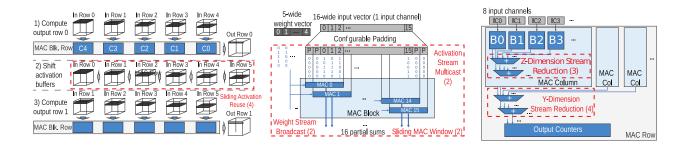

| 3.13 | Mapping of convolutional layers in MAC rows, and memory/stream generation             |    |

|      | amortization through data reuse. Shift-register organization emulating sliding        |    |

|      | window (left), MAC block with input/weight reuse and padding support (center),        |    |

|      | block organization implementing different levels of reduction (right)                 | 81 |

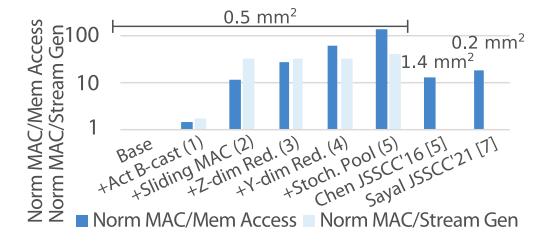

| 3.14 | Normalized ratio of MAC to memory accesses and stream generations compared            |    |

|      | to fixed-point designs. Accelerator area scaled to 14nm is included                   | 81 |

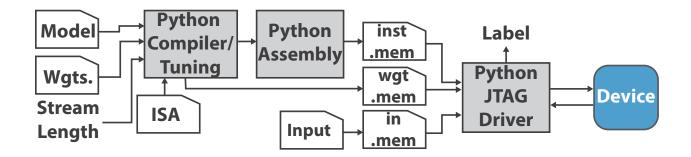

| 3.15 | Model deployment pipeline                                                             | 83 |

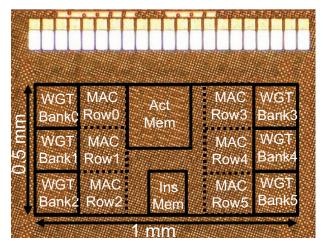

| 3.16 | Die shot and specifications                                                           | 84 |

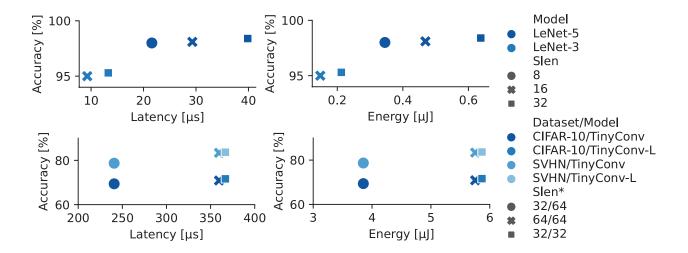

| 3.17 | Accuracy, latency (left), and energy (right) on the MNIST (top), SVHN and             |    |

|      | CIFAR-10 (bottom) datasets                                                            | 85 |

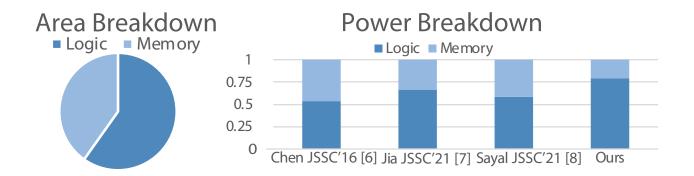

| 3.18 | Area (left) and power (right) breakdown, compared to [2, 3, 4]                        | 86 |

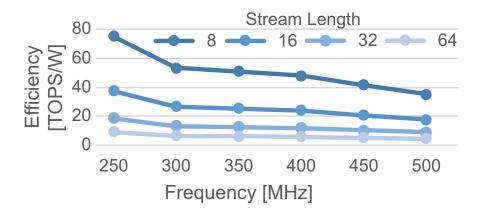

| 3.19 | Peak energy efficiency at different stream lengths                                    | 86 |

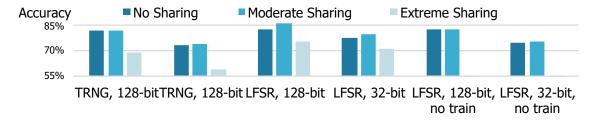

| 4.1  | Accuracy vs. sharing for TRNG and LFSR-based random number generation                 | 95 |

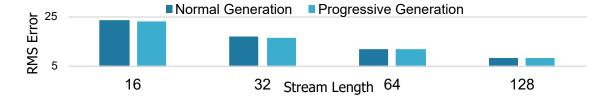

| 4.2 | Accuracy comparison between normal generation and progressive generation per-          |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | forming a multiplication of two uniformly sampled inputs. RMS Error is multi-          |     |

|     | plication error compared to an 8-bit integer                                           | 96  |

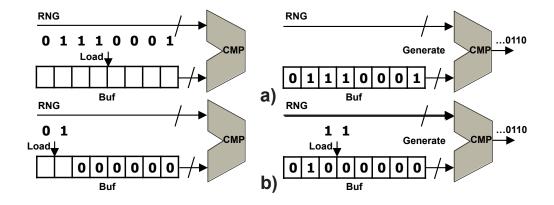

| 4.3 | Normal SNG (a) and progressive stream generation (b)                                   | 97  |

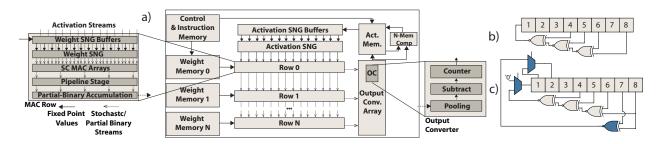

| 4.4 | Overall SC accelerator architecture block diagram. with breakdowns of the MAC          |     |

|     | row (left) and output converter (right) modules (a). Fixed 8-bit maximum length        |     |

|     | LFSR (b), and configurable 8- or 7-bit maximum length LFSR (c)                         | 98  |

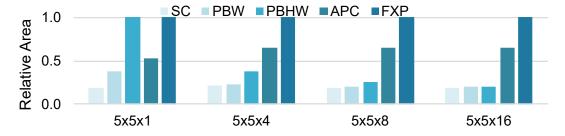

| 4.5 | Area comparison for different hardware implementations of SC-based MAC units           |     |

|     | for different kernel sizes and different levels of partial binary accumulation         | 100 |

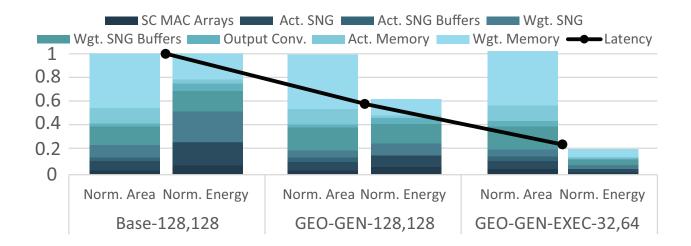

| 4.6 | Area, energy and latency for different GEO configurations (normalized to Base-         |     |

|     | 128,128)                                                                               | 107 |

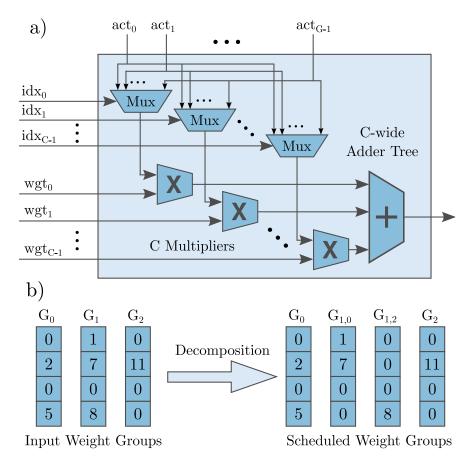

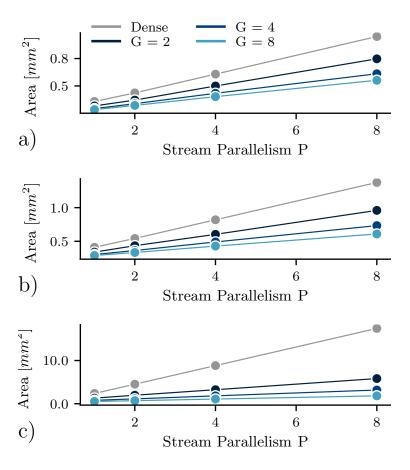

| 5.1 | Sparse PE with group size G and capacity C (a). Decomposing 3 arbitrary                |     |

|     | parameter groups of size $G = 4$ , into groups satisfying the capacity requirement     |     |

|     | of $C \leq 2$ (b)                                                                      | 116 |

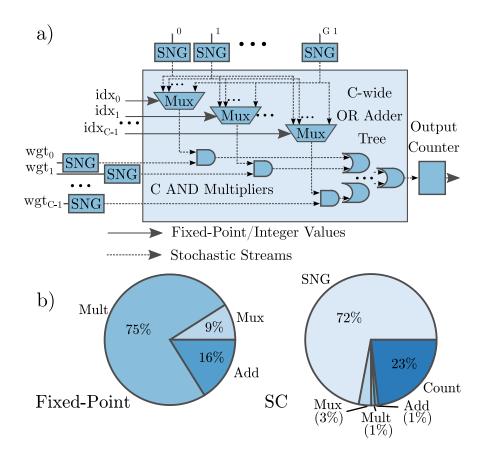

| 5.2 | Sparse GEO-style SC PE with group size G and capacity C (a). Split-Unipolar            |     |

|     | [5] logic is omitted case for readability. Area breakdown of fixed-point (left) and    |     |

|     | GEO SC (right) sparse PEs with G=4, and C=2 (b)                                        | 118 |

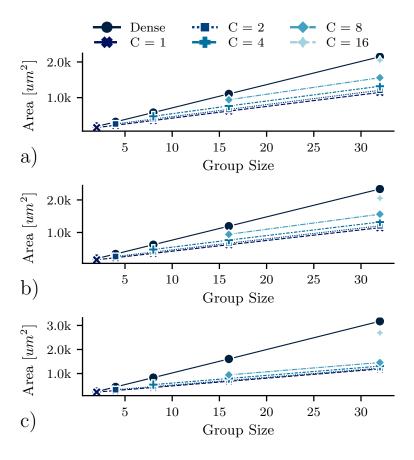

| 5.3 | Area of sparse and dense SC PEs, given different group sizes and capacities, for       |     |

|     | GEO (a), GEO with full binary accumulation (b), and uGEMM (c) style SC                 | 120 |

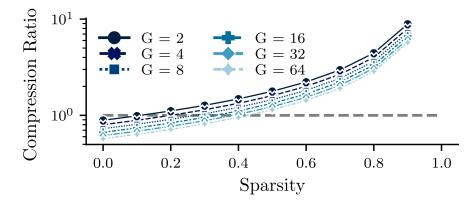

| 5.4 | Ideal ratio of dense to sparse storage cost for different PE group sizes, and sparsity |     |

|     | levels. Gray line shows the break-even point between sparse and dense storage          | 121 |

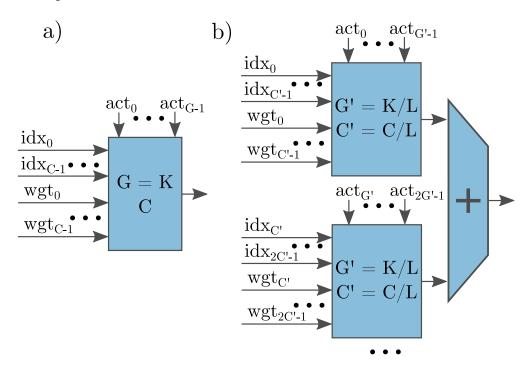

| 5.5 | Single-group sparse PE with a group size $G$ , capacity $C$ and dot product width      |     |

|     | K (a), and a throughput-equivalent multi-group sparse PE with $L$ groups               | 122 |

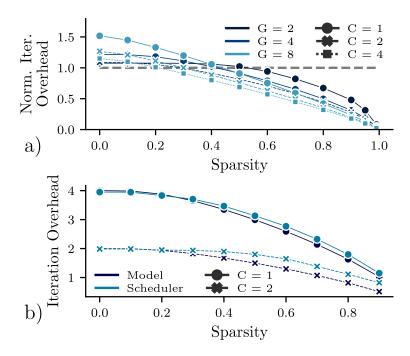

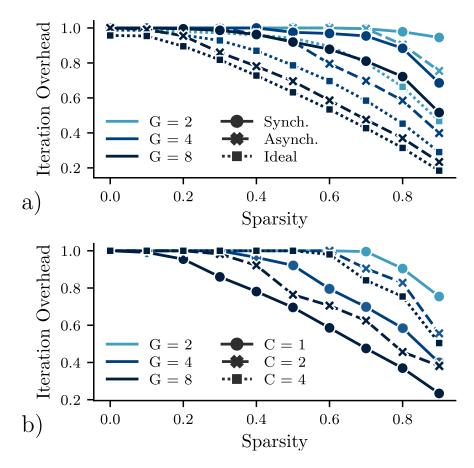

| 5.6  | Multi-group $K = 16$ sparse SC PE iteration overheads normalized to dense PE                   |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | area (GEO-style), for different group size $G$ and capacity $C$ , at different sparsity        |     |

|      | levels, estimated using the analytical model (a). Gray line shows the latency                  |     |

|      | break-even point with a dense PE. Iteration overhead difference between the                    |     |

|      | model and an ideal scheduler described in Section $5.4$ on the CIFAR-10 TinyConv               |     |

|      | network, for a PE with $G=4$ (b)                                                               | 125 |

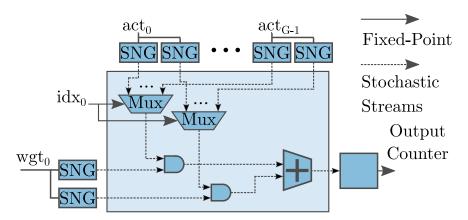

| 5.7  | Sparse SC PE with group size $G$ , capacity $C=1$ , and $P=2$ parallel streams.                |     |

|      | Split-unipolar accumulation fabric is omitted for readability                                  | 126 |

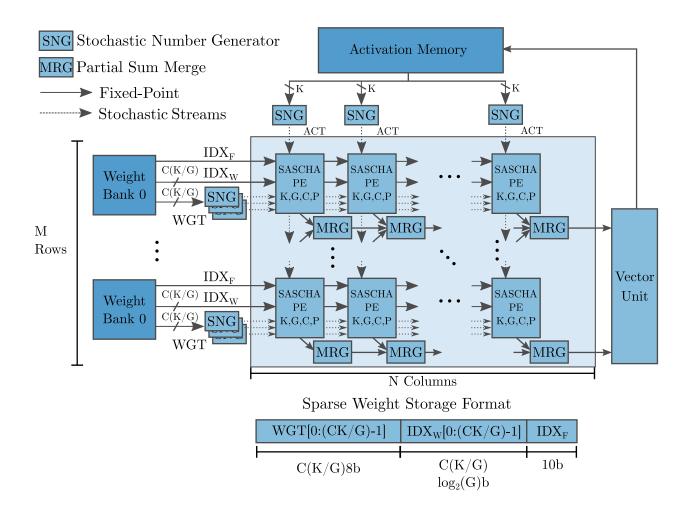

| 5.8  | Total area of a 32x32 array of $K=32~\mathrm{GEO}$ (a), GEO+ (b) and uGEMM (c)                 |     |

|      | PEs, dense and sparse, with different stream parallelism factors. $C=1$ for all                |     |

|      | sparse configurations                                                                          | 127 |

| 5.9  | SASCHA accelerator architecture block diagram. Partial sum output connections                  |     |

|      | were omitted for readability                                                                   | 129 |

| 5.10 | Three schedules of 5 partial filters, with $K=G=4$ and $C=1$ , on an architecture              |     |

|      | with $M=4$ rows: dense synchronous (a), sparse synchronous (b) and sparse                      |     |

|      | asynchronous (c). Crossed out boxed indicate compute under<br>utilization. $\ \ldots \ \ldots$ | 131 |

| 5.11 | Iteration overhead using different sparse scheduling methods (a) and different                 |     |

|      | group sizes and capacity using the sparse asynchronous scheduler (b)                           | 133 |

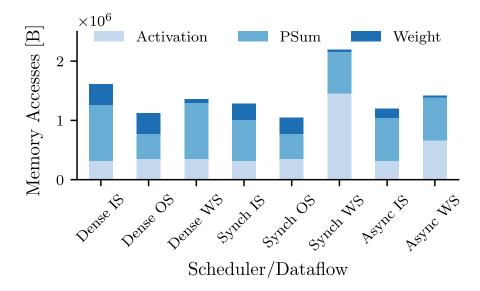

| 5.12 | Number of memory accesses in bytes for the convolutional layers of CIFAR-10                    |     |

|      | TinyConv network at 90% sparsity, depending on the choice of scheduling and                    |     |

|      | data<br>flow. All results for $M=32, N=32,$ and $K=32.$ Sparse results for                     |     |

|      | $G = 8, C = 1, \text{ and } P = 8. \dots$                                                      | 135 |

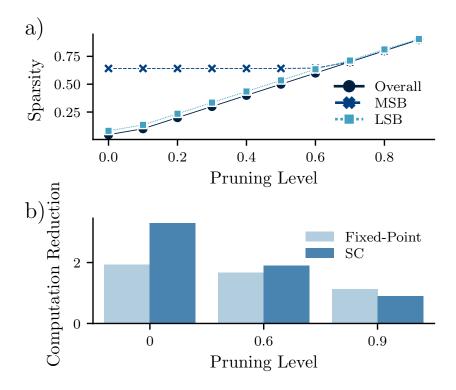

| 5.13 | Overall, MSB and LSB sparsity for (a) and reduction in sliced multiplication area              |     |

|      | x delay cost relative to non-sliced cost for SC and fixed-point (b), at different              |     |

|      | pruning levels for CIFAR-10 TinyConv                                                           | 136 |

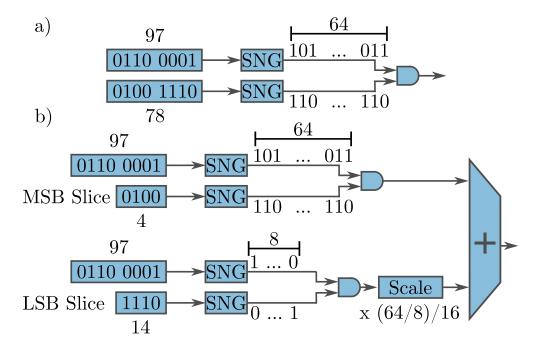

| 5.14 | SC unipolar multiplication a), and sliced multiplication b).                                   | 137 |

| 5.15 | Accuracy of CIFAR-10 VGG-11 with different sparsity levels. 0% sparsity means                                                                                                                                                           |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | no sparsity constraint                                                                                                                                                                                                                  | 139 |

| 5.16 | SASCHA CIFAR-10 Top-1 accuracy with dense and sparse networks                                                                                                                                                                           | 140 |

| 5.17 | SASCHA ImageNet Top-5 accuracy with dense and sparse networks                                                                                                                                                                           | 141 |

| 5.18 | Area (a) and power (b) breakdown of SASCHA GEO $8/1/8.$                                                                                                                                                                                 | 143 |

| 6.1  | Spinning Marker. This image shows event data generated from tossing a spinning whiteboard marker into the air with a cluttered background. The stationary background has disappeared so it is easy to see the moving objects. The white |     |

|      | events are positive events indicating an increase in brightness and the blue events                                                                                                                                                     |     |

|      | signal a decrease in brightness                                                                                                                                                                                                         | 153 |

| 6.2  | Analytical model parameters, for frame- (top), ROI- (middle), and event-based                                                                                                                                                           |     |

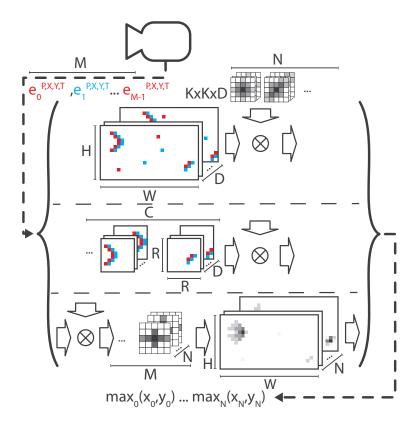

|      | (bottom) processing                                                                                                                                                                                                                     | 156 |

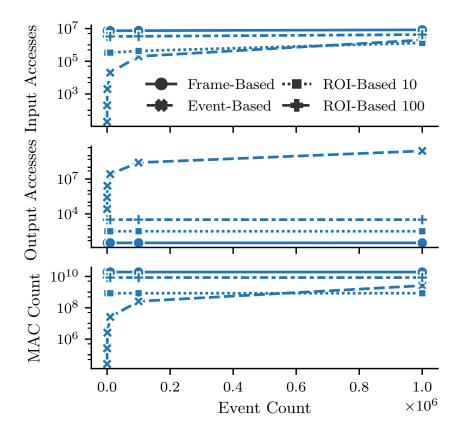

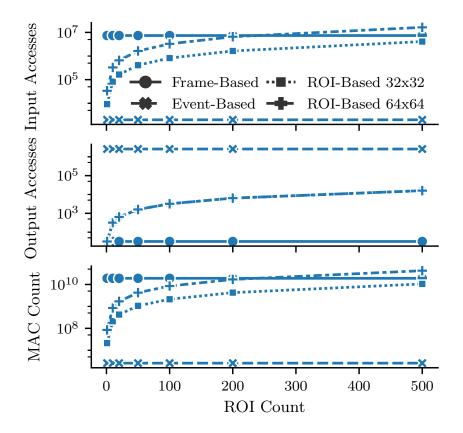

| 6.3  | Input (top) and output (middle) memory accesses, and MAC count (bottom),                                                                                                                                                                |     |

|      | with varying event count                                                                                                                                                                                                                | 157 |

| 6.4  | Input memory accesses (top), and MAC count (bottom), with varying ROI count.                                                                                                                                                            | 158 |

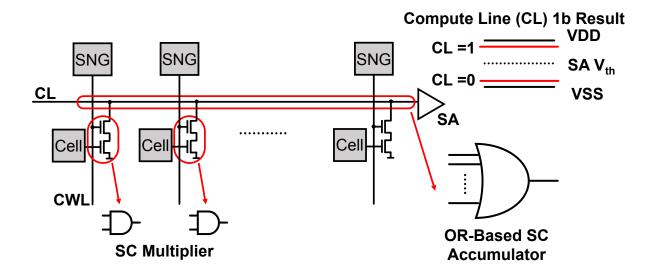

| 6.5  | 256-wide SCIM MAC structure                                                                                                                                                                                                             | 160 |

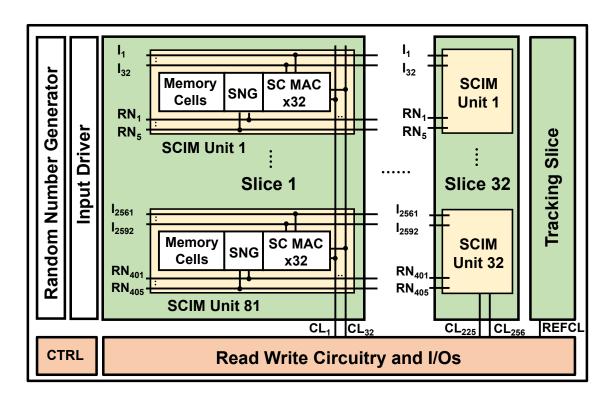

| 6.6  | SCIM Macro architecture                                                                                                                                                                                                                 | 161 |

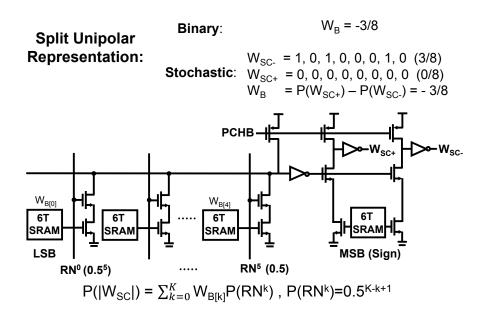

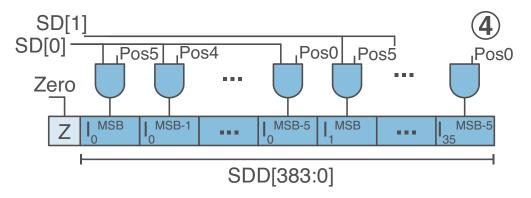

| 6.7  | Split-unipolar stochastic representation (top) and in-situ stochastic number gen-                                                                                                                                                       |     |

|      | erator (SNG) circuit (bottom)                                                                                                                                                                                                           | 163 |

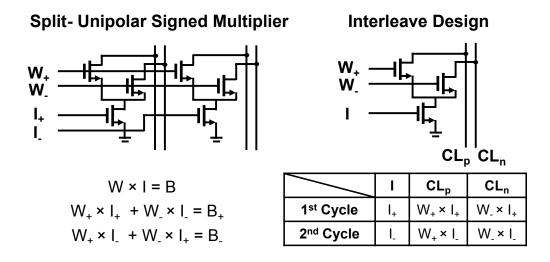

| 6.8  | Interleaved Signed SC MAC unit                                                                                                                                                                                                          | 165 |

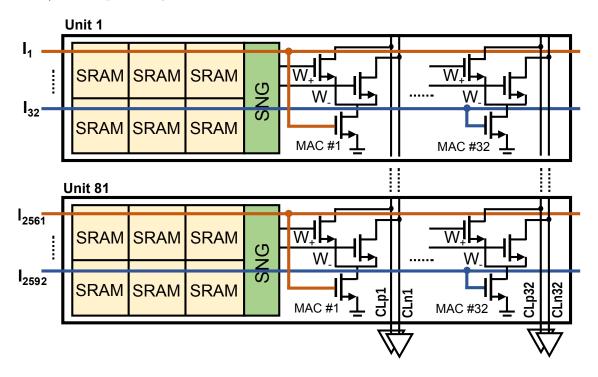

| 6.9  | SCIM Unit with 32 MAC reuse and SCIM slice                                                                                                                                                                                              | 166 |

| 6.10 | SCIMITAR architecture block diagram                                                                                                                                                                                                     | 167 |

| 6.11 | Transposed memory layout for 6-bit (top) and 1-bit (bottom) input data                                                                                                                                                                  | 169 |

| 6.12 | ROI memory requirements for different compression schemes                                                                                                                                                                               | 170 |

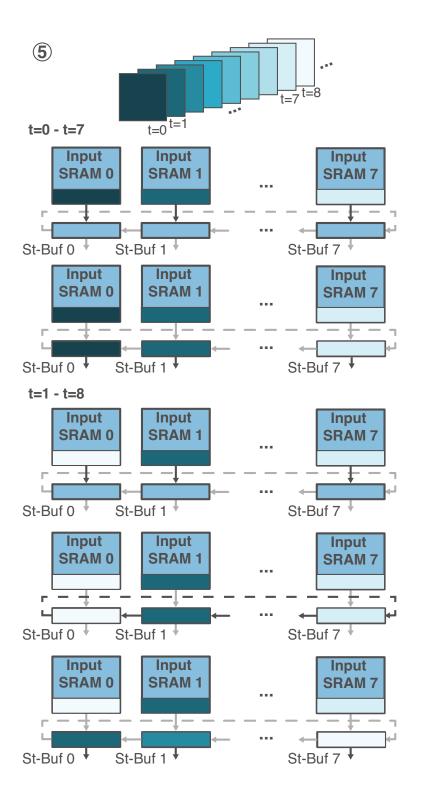

| 6.13 | Channel load skipping and half-row multiplexing using partitioned input SRAM.        | 171 |

|------|--------------------------------------------------------------------------------------|-----|

| 6.14 | Deserializing staging buffers with zero bit indicator                                | 172 |

| 6.15 | Time channel overlap support using circular staging buffers                          | 174 |

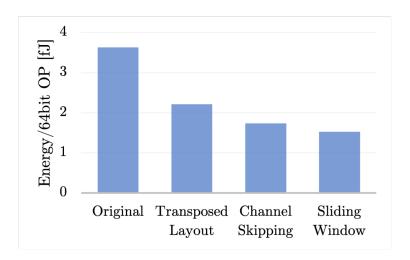

| 6.16 | Impact of proposed optimizations on computational energy efficiency of the SCIM-     |     |

|      | ITAR architecture. Efficiency calculated on 99% sparse input data assuming           |     |

|      | 64-bit long SC streams                                                               | 175 |

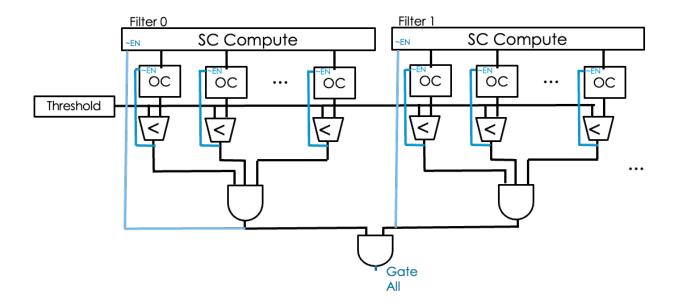

| 6.17 | Schematic implementation of 3-level early termination                                | 177 |

| 6.18 | SCIM Macro timing (top), and energy breakdown (bottom)                               | 180 |

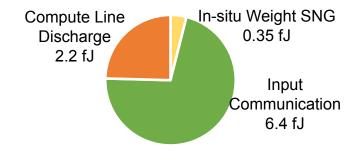

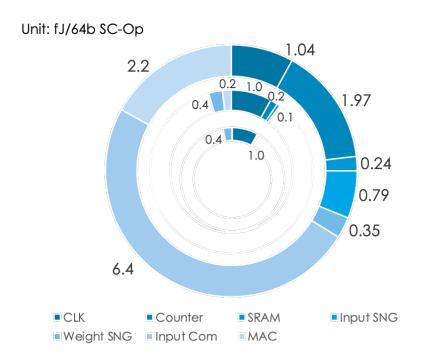

| 6.19 | Energy breakdown of the SCIMITAR components for dense (outer circle), $90\%$         |     |

|      | sparse (middle circle), and $99\%$ sparse (inner circle) workloads. Energy is calcu- |     |

|      | lated using 64-long stochastic streams                                               | 181 |

# LIST OF TABLES

| 2.1 | Hardware platforms used for the runtime experiments                                                                                               | 15  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Weight storage requirements of different networks depending on precision                                                                          | 16  |

| 2.3 | Benchmark models and datasets                                                                                                                     | 20  |

| 2.4 | Accuracy and network size (KB, in brackets) comparison                                                                                            | 38  |

| 2.5 | Runtime (ms) and energy (mJ, in brackets) for MNIST networks. A dash indicates a given model could not fit in memory                              | 41  |

| 2.6 | Runtime (ms) and energy (mJ, in brackets) for CIFAR-10/SVHN/Speech net-                                                                           |     |

|     | works. A dash indicates a given model could not fit in memory                                                                                     | 42  |

| 3.1 | Accuracy comparison between different pooling methods                                                                                             | 52  |

| 3.2 | ACOUSTIC control modules and their respective instructions                                                                                        | 66  |

| 3.3 | Accuracy comparisons                                                                                                                              | 70  |

| 3.4 | Performance comparison between ACOUSTIC LP and other fixed-point and stochas-                                                                     | -   |

|     | tic accelerators                                                                                                                                  | 74  |

| 3.5 | Performance comparison between ACOUSTIC ULP, MDL CNN [6] and Conv-RAM [7] on convolutional layers of LeNet-5 and CIFAR-10 CNN                     | 75  |

| 3.6 | FPGA utilization and performance comparison between ACOUSTIC ULP and other convolutional neural network accelerators. ACOUSTIC performance is for |     |

|     | stream lengths in range of 32 to 256-bits                                                                                                         | 77  |

| 3.7 | Datasets and models used in evaluation. Model sizes are limited by available                                                                      |     |

|     | on-chip memory.                                                                                                                                   | 84  |

| 3.8 | Comparison table                                                                                                                                  | 87  |

| 4.1 | Accuracy comparison with fixed-point, other SC implementations and so on                                                                          | 106 |

| 4.2 | Comparison between GEO ULP and fixed-point and neuromorphic implementa-                       |     |

|-----|-----------------------------------------------------------------------------------------------|-----|

|     | tions. Numbers are scaled to 28nm                                                             | 108 |

| 4.3 | Comparison between GEO LP and fixed-point and SC implementations. Numbers                     |     |

|     | are scaled to 28nm                                                                            | 109 |

| 5.1 | RMSE of unipolar multiplication with and without bit-slicing, w.r.t. floating-                |     |

|     | point precision, for different stream lengths (1000 trials). LSB stream length is             |     |

|     | 8                                                                                             | 138 |

| 5.2 | Area $[mm^2]$ , power $[mW]$ , throughput $[Fr/s]$ and energy-efficiency $[Fr/J]$ for dif-    |     |

|     | ferent accelerators, models and datasets, and sparsity                                        | 144 |

| 5.3 | Weight compression ratio for different SASCHA configurations, networks, and                   |     |

|     | sparsity levels                                                                               | 146 |

| 6.1 | Analytical event-based tracking performance model. <i>Event, frame</i> , and <i>ROI</i> refer |     |

|     | to event-, frame-, and ROI-based processing, respectively                                     | 156 |

| 6.2 | Average ROI processing latency in cycles, with and without early termination for              |     |

|     | different stream leangths                                                                     | 178 |

| 6.3 | Accuracy metrics of approximate computation in tracking applications using Ga-                |     |

|     | bor filters                                                                                   | 179 |

#### ACKNOWLEDGMENTS

As with anything worth doing in life, this dissertation is a result of years of hard work involving successes and moments of profound satisfaction but also struggles and disappointments. Most importantly, it is not a result of an individual toiling in isolation - I owe so much to so many people, it would be impossible to list them all here. Nevertheless, I will try my best, and I apologize to anyone who was omitted.

First and foremost, I want to thank my advisor, Professor Puneet Gupta. He showed faith in me by accepting me into his group, gave me all the support and resources I needed, and pushed me to accomplish my best. The volume and quality of the work presented here would not have been possible without his drive for excellence. Professor Gupta consistently shows the highest level of curiosity and tenacity when approaching any new topic or problem, something I aspire to emulate. Thanks to him, I have been exposed to a vast breadth of subjects that has expanded my horizons as a researcher, engineer, and technology enthusiast. I am truly grateful for his guidance and the opportunity to work with him.

I would also like to thank the other members of my doctoral committee: Professor Sudhakar Pamarti, Professor Mani Srivastava, and Professor Tony Nowatzki, for both teaching and research guidance. In particular, Professor Pamarti has been involved in the vast majority of the work presented here. He provided invaluable guidance on topics such as analog design, signal processing, and probability, without which this dissertation would hot have been possible. Professor Srivastava facilitated many productive discussions with the members of his group, and Professor Nowatzki introduced me to many new topics in computer architecture.

I would like to thank my internship managers, mentors, and coworkers. At Amazon's Annapurna Labs, I worked under the guidance of Patricio Kaplan and Paul Meyer, who introduced me to the world of cloud machine learning acceleration. At Facebook (now Meta), I had the pleasure of working with Rudy Tan and Piyush Agarwal, who exposed

me to the intricacies and challenges of designing AR/VR devices. Both internships were extremely rewarding and expanded my professional horizons. I would also like to thank my undergraduate and master's theses advisors: the late Dr. Jerzy Kasperek, and Dr. Paweł Rajda at the AGH University of Science and Technology. They introduced me to the field of research and gave me a chance to work on fascinating projects. I also want to thank my former mentors and coworkers, in particular Dilip Bansal (now with Intel) and Ali Rabbani (now with Apple) at Imagination Technologies, Dr. Toshiyuki Ikeda at NEC Corporation, and Dr. Marcin Szczurkowski at Elsta Elektronika. Learning from them has laid the foundations that made me ready to undertake doctoral studies.

Next, I would like to thank my collaborators, NanoCAD labmates, and fellow students: Tianmu Li, Dr. Saptadeep Pal, Dr. Irina Alam, Dr. Mark Gottscho, Dr. Wei-Che Wang, Shurui Li, Alexander Graening, Rhesa M. Ramadhan, Jiyue Yang, Vinod Kurian Jacob, Albert Lee, Yoo-Jin Chae, Dr. Steven Moran, Dr. Sumeet Singh, Professor Ankur Mehta, Swapnil Saha, Dr. Sandeep Singh, Rahul Garg, Trevor Black, Erin Askounis, Brian Zutter, and many more. They have all made my time at UCLA much more fulfilling and enjoyable. I also want to acknowledge my mentees: Tristan Melton, Feiqian Zhu, Siddharth Nandy, and Ravit Sharma. I might not have been the best mentor, but you all taught me a lot, and I hope I made a positive contribution to your career trajectories. My enormous gratitude goes out to UCLA Electrical and Computer Engineering staff, especially the irreplaceable Deeona Columbia, but also Jose Cano, Tricia Senate, and many others. Their efforts and dedication have been invaluable to this department, and me personally.

I could not have gotten here without the love, support, and encouragement of my parents, sister, and my maternal grandparents. Through good or bad, you made sure I was able to pursue my interests and made me the person I am today. My thanks also go to my friends, especially the ones I sometimes do not see for years, and then pick up exactly where we left off: Ewa Gadocha-Cios, Mateusz Tarnawa, and George Hawkins.

Finally, and most importantly, I would like to thank Dr. Camila Cendra, my wonderful

partner, who has been through it all with me. From being strangers in a strange land, through the highs and lows, the long distance, the longer distance, the pandemic, the two PhDs, across three continents, for over nine years, you have been my rock, my best friend, my soulmate.

### Copyrights and Re-use of Published Material

This dissertation contains significant material that has been previously published or is intended to be published in the future. Chapter 2 (3PXNet) contains material that was published in [8]. Chapter 3 (ACOUSTIC) includes material published in [5, 9]. Chapter 4 (GEO) appeared in [10]. Chapter 5 (SASCHA) appeared in [11]. Chapter 6 (SCIMITAR) is part of a paper which is under submission.

The copyrights on published research that re-appears in this dissertation is with either the IEEE and/or the ACM where appropriate. The respective copyright agreements allow for derivative works by the author with attribution, so no explicit permission was required for inclusion of material in this dissertation. The titles of each chapter have been changed somewhat to differentiate them from the published versions of the respective manuscripts where applicable.

Work explored in Chapters 2, 3, 4, and 5 has been done jointly with my labmate Tianmu Li, who has focused on the accuracy and training side, while I worked on architecture and implementation. Rahul Garg, Tristan Melton, and Jiyue Yang have contributed to the chip tapeout described in Chapter 3. Work described in Chapter 6 has been co-authored with Jiyue Yang, Vinod Kurian Jacob, and Alexander Graening. The former two focused on the analog circuit implementation, while the latter on the application side of tracking. Professor Puneet Gupta has contributed as a principal investigator (PI) to all of the work in this thesis, while Professor Sudhakar Pamarti served as a co-PI for the work described in Chapters 3, 4, 6.

Some of the work in my PhD that was conducted in collaboration with other individuals (where I contributed, but did not lead) are not included in the body of this dissertation.

Work presented in chapters 3, 4, 5, and 6 has been sponsored by the Air Force Research Laboratory (AFRL) and Defense Advanced Research Projects Agency (DARPA) under agreement number FA8650-18-27867. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of Air Force Research Laboratory (AFRL) and Defense Advance Research Projects Agency (DARPA) or the U.S. Government. Part of my PhD has been sponsored by the Fulbright Program under a Graduate Student Award, as well as through fellowships granted by the Electrical and Computer Engineering Department at UCLA.

### VITA

| 2012      | B.Eng. (Electronics and Telecommunication), AGH University of Science and Technology, Kraków, Poland.         |

|-----------|---------------------------------------------------------------------------------------------------------------|

| 2013      | M.Eng., Honors (Electronics and Telecommunication), AGH University of Science and Technology, Kraków, Poland. |

| 2013-2014 | Vulcanus in Japan Fellowship                                                                                  |

| 2014-2017 | Hardware Engineer, Imagination Technologies Ltd.                                                              |

| 2017      | Fulbright Graduate Student Award                                                                              |

| 2017      | Ph.D. Departmental Fellowship, ECE Department, UCLA                                                           |

| 2018      | Ph.D. Preliminary Examination Fellowship, ECE Department, UCLA                                                |

| 2020      | Digital Design Intern, Facebook Inc. (now Meta Platforms Inc.)                                                |

| 2022      | ASIC Design Intern, Amazon Web Services Inc.                                                                  |

### **PUBLICATIONS**

Wojciech Romaszkan, Tianmu Li, and Puneet Gupta, "3PXNet: Pruned-Permuted-Packed XNOR Networks for Edge Machine Learning," in *ACM Transactions on Embedded Computing Systems (TECS)* 19, no. 1, pp. 1-23, 2020.

Wojciech Romaszkan, Tianmu Li, Tristan Melton, Sudhakar Pamarti, and Puneet Gupta, "ACOUSTIC: accelerating convolutional neural networks through or-unipolar skipped stochastic computing," in 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, pp. 768-773, 2020.

Tianmu Li, Wojciech Romaszkan, Sudhakar Pamarti, and Puneet Gupta, "GEO: Generation and Execution Optimized Stochastic Computing Accelerator for Neural Networks," in 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, pp. 1-6, 2021.

Shurui Li, **Wojciech Romaszkan**, Alexander Graening, and Puneet Gupta, "SWIS - Shared Weight blt Sparsity for Efficient Neural Network Acceleration," in *First International Research Symposium on Tiny Machine Learning (tinyML)*, Burlingame, USA, pp. 1-8, 2021.

Wojciech Romaszkan, Tianmu Li, Rahul Garg, Jiyue Yang, Sudhakar Pamarti, and Puneet Gupta, "A 4.4-75-TOPS/W 14-nm Programmable, Performance-and Precision-Tunable All-Digital Stochastic Computing Neural Network Inference Accelerator," in *IEEE Solid-State Circuits Letters* 5, pp. 206-209, 2022

Wojciech Romaszkan, Tianmu Li, and Puneet Gupta, "SASCHA—Sparsity-Aware Stochastic Computing Hardware Architecture for Neural Network Acceleration," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 41, pp. 4169-4180, no. 11, 2022

Jiyue Yang, Tianmu Li, **Wojciech Romaszkan**, Puneet Gupta, and Sudhakar Pamarti, "A 65nm 8-bit All-Digital Stochastic-Compute-In-Memory Deep Learning Processor," in 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 10-11, 2022

# CHAPTER 1

### Introduction

In the last decade, the computing landscape has been engulfed by chaos. The looming deprecation of Moore's Law has created a demand for new devices, architectures, and algorithms to deliver the steady stream of performance improvements on which the markets have relied for decades [12]. At the same time, the rapid emergence of deep learning has created a massive demand for domain-specific computational power across both cloud and edge computing [13, 14, 15]. The existing infrastructure struggles to satisfy this demand, particularly at the edge, where deep learning's hunger for FLOPs and MBs goes against tight latency, energy, and privacy constraints [16]. Those conditions have created a perfect storm of opportunity for introducing new hardware architectures, especially at the edge, where silicon real estate is traditionally very scarce. Indeed, smartphone SoC with various "neural engines" are proliferating the markets as we speak [17].

Coupled with the above circumstances is the fact that deep learning algorithms have been shown to be incredibly approximation tolerant [18, 19, 20]. This tolerance has opened a pandora's box of new and old techniques, such as pruning or quantization, and hardware approaches, including spiking, neuromorphic, in-memory, and stochastic computing, among others [21, 22, 23, 24, 2, 25, 26]. What they all have in common is a promise of driving down deep learning model sizes and computational costs, enabling their widespread deployment in edge devices. The work in this dissertation explores, combines, and evolves those techniques to enable the development of future highly-compact and highly-efficient architectures and algorithms for deep learning.

The remainder of this Section provides a brief overview of the topics that form the foundation of this dissertation. Section 1.1 provides an introduction to neural network model compression, including quantization and pruning, as well as existing methods of model deployment on edge devices. Section 1.2 introduces stochastic computing and its intricacies. Section 1.3 discusses the rapidly growing field of domain-specific accelerators, particularly those targeting neural networks. Finally, Section 1.4 summarizes the work presented in this dissertation.

### 1.1 Model Compression: Better, Faster, Smaller

Ever since the staggering success of AlexNet in the ImageNet visual recognition challenge, deep learning models have been evolving at a rapid rate [27, 28]. Vision models based on convolutional layers quickly reached tens of giga-operations (GOPS) and tens if not hundreds of megabytes (MBs), in size [29, 30, 1, 31]. With complexity, their capabilities grew, becoming a force multiplier for edge devices, like smartphones or sensors [32, 33, 34]. However, this growing demand for resources made deploying those models restrictive, if not outright prohibitive, on those same devices [16]. And thus, a simple question - "how do we make the models smaller?" has preoccupied countless researchers for the better part of the last decade, yielding many ingenious solutions [35]. This Section aims to present a high level summary of those. A general introduction to deep neural networks is omitted for brevity, but readers not familiar with the topic can refer to [29, 36].

### 1.1.1 Fewer Bits - Quantization & Binarization

One of the first crucial insights into model compression was the realization that 32-bit floating-point precision, ubiquitous in scientific computing, was not necessary for highly redundant and error resilient deep learning models [14, 2]. Multiple works have shown that decreasing precision of underlying computation through quantization does not affect accu-

racy while significantly improving storage and runtime [37, 38, 39, 40, 19, 14]. A quick progression of lower precision models and libraries followed - 16-bit floating point [41], 16-bit fixed-point [2], 8-bit fixed-point [42], and below [19, 42, 24]. To reduce computational complexity to its absolute limit, researchers have proposed binarization, which restricted all values to -1 and +1 [43, 44, 45, 18, 46]. Those Networks are commonly referred to as XNOR-Nets, because multiplication between binarized values can be implemented using a bitwise XNOR operation.

The promise of significant performance and storage improvements given by XNOR-Nets has resulted in multiple software and hardware implementations. Umuroglu et al. have created FINN [47], a framework for binarized FPGA accelerators, further expanded to support larger models by Fraser et al. [48]. Other binarized accelerators have been proposed, both targeting FPGAs [49, 50, 51, 52], ASIC [53, 54, 55, 56], and in-memory compute [57, 58]. Yang et al. [59] have developed BMXNet, an extension of MXNet [60] based on binarized GEMM kernel. Depth-first binarized convolution implementations have also been shown for both CPUs and GPUs [61, 62, 63].

#### 1.1.2 Alternate Number Representations

Besides quantization, researchers have explored alternative ways of representing numbers. One of them is the so-called *unary* computing. Compared to *binary* numbers, like fixed- or floating-point, where each bit has a positional significance, unary numbers are streams of bits with identical significance [64]. There are two types of unary numbers: rate- and temporal-coded. In the former, the value is encoded in a frequency of an event, e.g., the number of 1s in a stream. Rate-coded unary computation is commonly known as stochastic computing (SC). Since SC is a major focus of this dissertation, a more comprehensive introduction is provided in Section 1.2. Temporal coding encodes the information into the timing of a signal transition, with a stream consisting of a series of 1s followed by a series of 0s. Temporal coding can be performed within the stream generator, using the so-called thermometer coding

[65], or by designing paths with different delays, referred to as race-logic [66]. Compared to rate coding, temporally-coded numbers either do not have essential functional units or those units are highly inefficient. Further, temporal coding lacks many opportunities for improving accuracy possible in SC [67].

Other number representation methods are tied to the hardware implementation. A large body of work tries to imitate the behavior of the human brain through spiking neuron connectivity [26, 68, 69, 70]. Spiking hardware, commonly referred to as neuromorphic, represents data using the timing or frequency of the pulses, instead of their amplitude. This can be implemented in the digital or analog domain. Examples of the former include IBM TrueNorth [26], the SpiNNaker Project [68], and Bluehive [71]. Analog spiking hardware examples are: Neurogrid [69], HICANN [70], and CAVIAR [72]. While neuromorphic hardware has potential advantages, like energy efficiency, and on-device training using synaptic plasticity, they are also notoriously hard to train and scale [73]. Pulse width modulation (PWM) has also been used as a way of representing values for more efficient analog hardware implementations [6].

There are also purely digital alternative representations. Posit format has been proposed as an substitute for floating-point, offering variable-width exponent and fraction fields, higher dynamic range, and more efficient hardware implementations [74]. While some devices offer posit support, it has not yet been broadly adopted [75, 76]. Apart from that, various form of non-linear quantization have been proposed beyond fixed-point, often requiring custom software or hardware support [77, 24, 78].

#### 1.1.3 Fewer Values - Sparsity & Pruning

The other realization foundational to model compression was that in computation based on linear algebra, multiplications involving a zero will not contribute to the final result, hence can be skipped [79]. The underlying computation then becomes *sparse*. While it applies to both weights and activations, the opportunities and mechanisms involved are

different. Zero-valued weights are enabled through the process of pruning the model, which involves removing connections in the model that are deemed inconsequential. It was first proposed over 20 years ago as a way of improving generalization and reducing computational complexity for both training and inference [22, 80]. Since activations are dynamic, they cannot be pruned statically in the same manner. However, activations can be effectively sparsified through the use of the popular rectified linear unit (ReLU) activation function [79, 81]. Once weights, activations, or both, are made sparse, in theory, it is possible to skip both storage and computation involving zero values. Recently, Han et. al. [82] have shown over 10x compression on popular network models with no increase in error rates. By further coupling pruning with quantization and efficient coding in a scheme called Deep Compression, they achieved up to 49x size reduction [83]. However, deploying pruned models on highly-parallel architectures has proven problematic due to the storage overhead and irregular memory access patterns of sparse matrix multiplication [21, 84].

To make pruning more regular, multiple forms of "structured" pruning have been proposed. Lebedev and Lempitsky [85] proposed group-wise sparsification. Foroosh et. al. [86] hard-coded the sparsity patterns into the source code, achieving up to 6.88x speedup on CPUs. Anwar et. al. [87, 88] explored different granularities of pruning: feature map, kernel, and intra-kernel and introduce kernel strided sparsity. Sredojevic et. al. [84] have proposed an algorithmic way of inducing regularity in sparse networks. Yu et. al. [21] have developed a hardware-aware pruning method called Scalpel, which matches the coarseness of pruning to the parallelism of the underlying hardware. Wang et. al. [89] have used structured sparsity in unrolled kernels after im2col conversion. Pruning has been successfully exploited in custom accelerators by using compressed storage, skipping memory accesses, gating computation, and exploiting novel dataflows [13, 90, 79, 19]. Crossbar-aware pruning has also been proposed given the recent emergence of analog crossbar-based accelerators [91].

#### 1.1.4 Edge Models & Libraries

Edge Machine Learning inference on embedded platforms has been explored in recent years as a way to remove the communication energy and latency involved in offloading it to the servers. Due to severe memory and energy constraints of such devices, various model compression techniques have been used to make such applications feasible. Compressed Neural Network models like SqueezeNet [92], ShuffleNet [93], and MobileNet [94] have been developed, specifically targeting low memory footprints. Lai et. al. [95], have developed CMSIS-NN, a software library for ARM Cortex-M microcontrollers with 8- and 16-bit fixed-point support. Microsoft is developing EdgeML, a Machine Learning library containing algorithms optimized for low storage, energy and latency [96, 97]. Google has create TensorFlow Lite, and extension of the TensorFlow framework targetting microcontroller class devices [98]. Other examples include Apache microTVM, STM Cube.AI, Synopsys embARC, and MIT MCUNet [16, 99].

# 1.2 Stochastic Computing - Processing with Random Streams

Stochastic Computing (SC), introduced by [100] in the 1960s, is a number representation system. It uses a proportion of 1's in a binary stream to represent fractional numbers. Compared to conventional fixed- or floating-point formats, SC makes it possible to implement certain arithmetic operations, like multiplication and addition, using single logic gates, and is highly error-tolerant [101]. However, the compact arithmetic offered by SC comes at the cost of random errors and precision issues, which make it unsuitable for applications requiring high numerical precision[102]. Because of that, SC found its niche in error-tolerant applications, like image processing [102] and Discrete Fourier Transform [103]. Fortunately, neural networks' error-tolerant nature, as well as heavy reliance on linear algebra kernels and multiply-accumulate (MAC) operations, make them perfect candidates for SC acceleration [5, 64, 104]. Because of that, SC has been enjoying a renaissance, with many different flavors

of computation proposed, spanning various points on the accuracy-efficiency spectrum - some of them maximizing the density and efficiency, while others maintaining the accuracy close to fixed-point designs [5, 10, 64, 105, 104]. Below we briefly outline the most relevant components of SC.

### 1.2.1 Number Representation

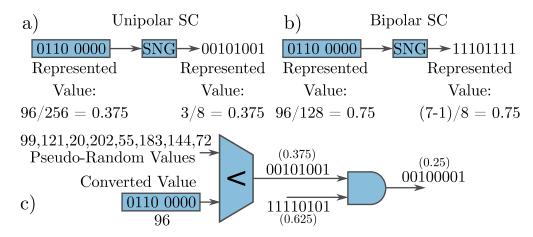

Stochastic computing offers two alternative number representation formats: unipolar and bipolar. In the former, a value in the range of [0,1) is represented as the proportion of 1's in a binary stream of arbitrary length, as shown in Figure 1.1a). The latter, shown in Figure 1.1b), represents a number in the range of (-1,1) using the difference between the number of 1's and 0's in the stream. The streams are generated by comparing the possibility with a uniformly-distributed random number in [0,1). The stream generation circuits are commonly referred to as stochastic number generators (SNGs), consisting of a pseudo-random number source, e.g., a linear feedback shift register (LFSR) and a comparator [100], as shown in Figure 1.1c). Converting back to the binary domain can be done using a counter for unipolar representation.

Figure 1.1: Examples of unipolar (a) and bipolar (b) SC representation, and a unipolar Stochastic Number Generator Circuit (SNG) with an AND gate SC multiplication (c).

In neural networks, maintaining high accuracy mandates using weights with both positive and negative values, which makes bipolar representation historically the most common choice when implementing SC-based accelerators [106, 107, 105]. However, [108] noticed that using unipolar representation results in higher accuracy compared with bipolar. Higher precision comes from the fact that the value of a unipolar bitstream has equivalent distribution to a binomial distribution divided by the length of the bitstream, so the root mean square (RMS) error can be represented as:

$$E_u = \frac{\sqrt{n_u v(1-v)}}{n_u} = \sqrt{\frac{v(1-v)}{n_u}}$$

(1.1)

Where  $E_u$  is the error, and  $n_u$  is the length of the unipolar bitstream. Error of bipolar stream can be calculated similarly as:

$$E_b = \sqrt{\frac{1 - v^2}{n_b}} \tag{1.2}$$

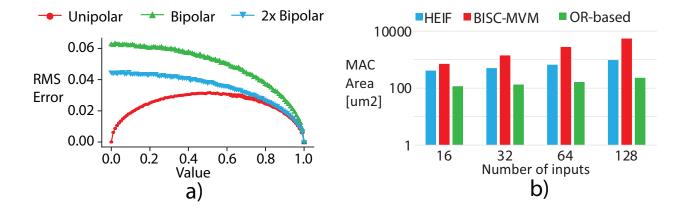

Where  $E_b$  is the error, and  $n_b$  is the bitstream length. To have the same RMS error for both representations,  $n_b = n_u \times (1+v)/v$ , and (1+v)/v > 2 for 0 < v < 1. Consequently, the bipolar representation will always require > 2X bitstream length to represent the same value with the same accuracy compared to unipolar representation. Figure 1.2a) shows the simulated error of software-generated stochastic numbers across 10,000 runs for different values, confirming the theoretical results. Because of that, recent works have embraced unipolar representation with extensions to make using negative numbers possible [109, 110].

#### 1.2.2 Multiplication and Accumulation

One of the main selling points of SC is that it can perform computation using bit-wise operations between two input bitstreams. To explain the reason behind that, consider stochastic numbers as probabilities. For example, an AND gate performs  $AND(v_1, v_2) = v_1 \times v_2$ , where  $v_1, v_2$  are the input possibilities for two unipolar streams. Similarly, a 2:1 multiplexer

Figure 1.2: RMS error of the bit stream representation for a given value a), and area  $[\mu m^2]$  comparison between different SC MACs, depending on the number of inputs b).

(MUX) can be used to compute a scaled addition between two inputs:  $MUX(v_1, v_2, s) = s \times v_1 + (1 - s) \times v_2$ , where s is the select input. For a bit-wise computation, each output bit follows a Bernoulli distribution with a mean equal to the expected value if input bits are independent. As a result, the output accuracy of bit-wise computation has the same accuracy as generating the same number directly. This observation allows the modeling of output error using only the expected output value without worrying about input values and computation performed.

Accumulation has historically been an issue when applying stochastic computing to neural networks, mainly due to precision [106]. Multiplexer can act as a stochastic adder by using a 50% random stream at the select input. However, multiplexer-based addition suffers from two critical issues: it requires the generation of an additional random stream and scales down the result by two compared to typical addition. Sharing a random sequence can alleviate the former problem. The latter issue degrades the accuracy of computation, mainly when performing extensive accumulation. Since neural networks generally perform very large matrix multiplications, fully stochastic MUX-based addition is not suitable for those without a significant increase in the stream length [106]. Because of that, prior works in SC-based

neural network acceleration were often forced to perform accumulation in the fixed-point domain, by either using costly approximate parallel counters (APCs) [106] or converting the results every multiplication [107].

An alternative way of stochastic accumulation, OR-based accumulation, has been proposed in [111]. It is scaling-free (important for extensive accumulations in DNNs), and also much more compact than alternative accumulation methods. However, it has reasonable accuracy only for unipolar streams. This property has made it largely disregarded in prior SC work [106]. Figure 1.2b) shows the comparison of the MAC area for two prior state-of-the-art methods, SC-DCNN/HEIF [106, 105] and BISC-MVM [107] to OR-based MAC for a different number of inputs synthesized using a commercial 28nm library. SC-DCNN/HEIF uses APC-based accumulation, while BISC-MVM converts results to fixed-point binary after every multiplication. As can be seen, OR accumulation can be as much as 4.2x and 23.8x more compact than SC-DCNN/HEIF and BISC-MVM, respectively. As we will show in Section 3.3.1, taking advantage of computational density is vital to reap the full benefits of-fered by SC, which is why using OR-based accumulation is so important. However, a major issue with it is that it is not an exact addition. For a two-input OR, the result is equal to v1+v2-v1v2 instead of v1+v2. We show later how we address this imperfect accumulation in the training of the networks.

### 1.2.3 Stochastic Neural Network Functions

More complicated operations, like neural network activation functions, are often implemented using finite-state machine (FSM) circuitry [106, 105]. Many recent efforts have been directed towards finding optimal SC representations for particular operations [112, 113, 114, 115]. Another essential operation is max pooling, which is the most commonly used method of dimensionality reduction in neural networks [27, 1]. Although prior works have shown successful implementation of max pooling in SC [106, 108, 116], it usually requires a finite state machine (FSM), which increases the area and energy cost of SC. In contrast, to implement

average pooling, only a single multiplexer exploiting the scaled addition property is required. For example, [116] have shown that replacing max with average pooling, can reduce the area and power of a stochastic convolutional engine by up to 2.02x and 1.94x respectively.

# 1.3 Domain-Specific Acceleration - Breaking the Shackles of Generality

Even apart from the emergence of deep learning, the need for domain-specific (DS) computing has been widely recognized [12, 117]. However, the rapid popularization of first vision [27, 1, 30], and then language models [118, 119], made the adoption of DS accelerators a priority. Initial approaches, like Eyeriss [2] and DianNao [120], focused on reducing the precision of computation from floating- to fixed-point, and optimizing dataflows targeted at convolutional neural networks (CNNs). From there on, multiple different approaches followed. Some focused on finding new hardware opportunities in quantization, in particular using bit-serial arithmetic, which serially processes fixed-point numbers, one bit position at a time. Examples of such accelerators include Stripes [19], UNPU [121], Laconic [122], and Pragmatic [123], and Bit Fusion [124]. There are also binary and ternary hardware accelerators, listed in Section 1.1.1. Others have tried designing architectures oriented around exploiting sparsity, like SCNN [79], EIE [81], NullHop [125], GoSPA [126], SparTen [127], and Tensaurus [128], among others. A more comprehensive discussion of sparse accelerators is presented in Chapter 5. Extensive work has also been done on optimizing dataflows [129, 130], and scale-out architectures [15, 131].

Given the limits of efficiency within the digital domain, and highly regular, dot-product-based arithmetic involved in neural networks, people quickly recognized the potential of analog computation. Neuromorphic approaches have already been discussed in Section 1.2.1. However, they were quickly overshadowed by non-spiking analog accelerators based on the idea of compute-in-memory (CIM) [132]. They combine the advantage of the advantage of

dense and efficient analog computation, with reduced data movement, as one of the operands does not need to leave the memory. Different types of memory cells can be used, providing different benefits [132, 133, 56, 134, 135, 136, 137, 138]. This is an extensive field, and while more details are provided in Chapter 6, interested readers should refer to [25].

# 1.4 Dissertation Outline

The research in this dissertation was motivated by a single goal: enabling ever-larger deep learning models to run on even the most resource-constrained edge devices. This goal is achieved by identifying the most promising techniques, coming up with novel solutions that address their shortcomings, combining them in a synergistic manner, and creating efficient highly hardware and software implementations.

This dissertation is organized as follows:

- Chapter 2 describes 3PXNet Pruned, Permuted, Packed XNOR Networks, which combine binarization and pruning to deliver usable neural network models deployable on the most tightly constrained platforms.

- Chapter 3 proposes ACOUSTIC Accelerating Convolutions through OR-Unipolar Skipped Stochastic Computing, the first system-level accelerator architecture that attempts to maximize the synergies of deep convolutional neural networks and stochastic computing. A 14nm demonstration chip is also demonstrated.

- Chapter 4 presents GEO Generation and Execution Optimized Stochastic Computing Accelerator for Neural Networks. GEO addresses the main shortcomings of ACOUSTIC, through novel algorithmic and architectural solutions.

- Chapter 5 describes SASCHA Sparsity-Aware Stochastic Computing Hardware Architecture for Neural Network Acceleration a first accelerator that combines both

stochastic computing and weight sparsity support by solving a series of non-trivial implementation challenges to enable a new frontier in energy-efficiency.

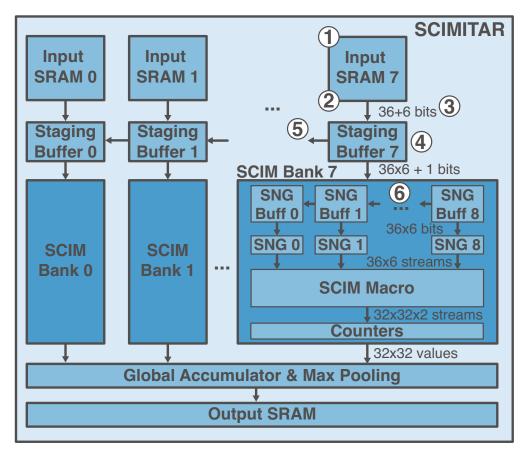

- Chapter 6 presents SCIMITAR an event-based, stochastic compute in-memory accelerator architecture. It synergistically merges SC with the emerging field of in-memory computation, while enabling support for highly-sparse event-based data processing.

- Finally, **Chapter 7** summarizes the contributions of this dissertation, and describes its possible future extensions.

CHAPTER 2

3PXNet - Fewer Bits, More Zeros

As the adoption of Neural Networks continues to proliferate different classes of applications

and systems, microcontroller-based edge devices have lingered behind. Their strict energy

and storage limitations make them unable to cope with the sizes of popular neural network

models. While many compression methods, such as precision reduction and pruning, have

been proposed to alleviate this, they do not go quite far enough. To push size reduction to its

absolute limits, we combine binarization with sparsity in Pruned-Permuted-Packed XNOR

Networks (3PXNet), which can be efficiently implemented on even the smallest of embedded

microcontrollers. 3PXNets can reduce model sizes by up to 38X and runtime by up to 3X

compared with already compact conventional binarized implementations with less than 3%

accuracy reduction. We have created the first software implementation of sparse-binarized

Neural Networks, released as an open-source library targeting edge devices. Our library is

complete with training methodology and model generating scripts, making it easy and fast

to deploy.

Collaborators:

• Tianmu Li, Electrical and Computer Engineering, UCLA.

• Professor Puneet Gupta, Electrical and Computer Engineering, UCLA.

Source code available at: https://github.com/nanocad-lab/3pxnet/

14

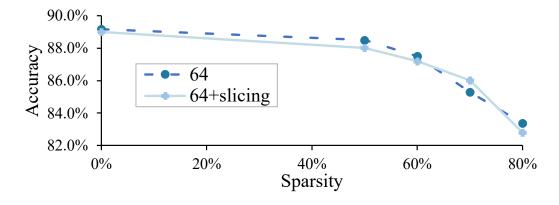

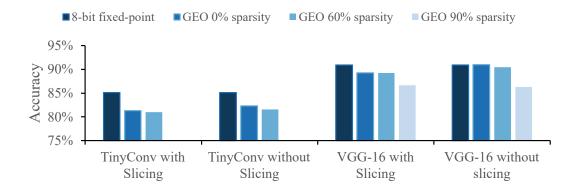

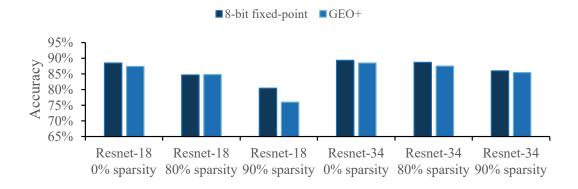

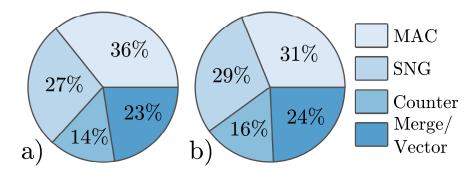

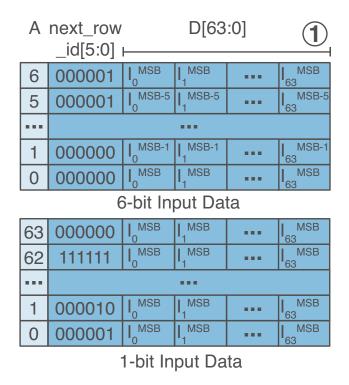

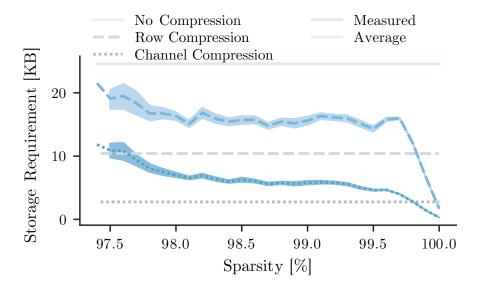

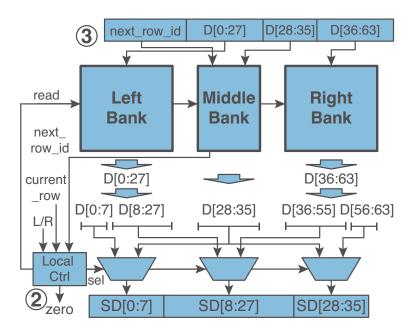

# 2.1 A Case for Sparse XNOR Networks