# Detailed Placement for Enhanced Control of Resist and Etch CDs

Puneet Gupta, *Member, IEEE*, Andrew B. Kahng, *Senior Member, IEEE*, and Chul-Hong Park, *Student Member, IEEE*

Abstract-Subresolution assist feature (SRAF) and etchdummy insertion techniques have been absolutely essential for process window enhancement and CD control in photo and etch processes. However, as focus levels change during lithography manufacturing, CDs at a given "legal" pitch can fail to achieve manufacturing tolerances. Placed standard-cell layouts may not have the ideal whitespace distribution to allow for an optimal assist-feature insertion. This paper first describes a novel dynamic programming-based technique for Assist-Feature Correctness (AFCorr) in detailed placement of standard-cell designs. At the same time, etch-dummy features are used in the mask data preparation flow to reduce CD skew between resist and etch processes and to improve the printability of layouts. However, etch-dummy rules conflict with the SRAF insertion because each of the two techniques requires specific design rules. We further present a novel SRAF-aware etch-dummy insertion method (SAEDM) which optimizes the etch-dummy insertion to make the layout more conducive to the assist-feature insertion after the etch-dummy features have been inserted. Since placement of cells can create forbidden-pitch violations of resist process and can increase etch skew, the placer must also generate etchdummy-correct placement. This can be solved by Etch-dummy Correctness (EtchCorr), which is an intelligent whitespace management for etch-dummy-corrected placement, an extension of the AFCorr methodology. These methods for enhanced resist and etch CD control are validated on industrial test cases with respect to wafer printability, database complexity, and device performance. For benchmark designs, we validate the four methodologies: 1) AFCorr; 2) SAEDM; 3) AFCorr + SAEDM; and 4) AFCorr + EtchCorr + SAEDM. The AFCorr placement perturbation achieves a significant reduction in forbidden pitches between polysilicon shapes. Using 1) flow, forbidden-pitch count of photo process is reduced by 76%-100% for 130 nm and by 87%-100% for 90 nm. Our novel Corr design-perturbation technique, which combines the AFCorr and EtchCorr methods, facilitates additional SRAF and etch-dummy insertions and, thus, reduces the CD skew between the photo and etch processes. After Corr with SAEDM, edge placement error (EPE) count is also reduced by 91%-100% in the resist CD and by 72%-98% in the etch CD. Our methods provide a substantial improvement in CD control with negligible timing, area, and CPU overhead. The advantages

Manuscript received February 14, 2006; revised July 24, 2006 and November 11, 2006. An earlier version of this paper appeared in [7]–[9]. This paper was recommended by Associate Editor D. Z. Pan.

P. Gupta was with the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093-0409 USA. He is now with the Department of Electrical and Computer Engineering, University of California, Los Angeles, CA 90095 USA (e-mail: puneet@ee.ucla.edu).

A. B. Kahng is with the Department of Computer Science and Engineering and the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093-0114 USA (e-mail: abk@ucsd.edu).

C.-H. Park is with the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, CA 92093-0409 USA (e-mail: chpark@vlsicad.ucsd.edu).

Digital Object Identifier 10.1109/TCAD.2007.906998

of such correctness methods are expected to increase in future technology nodes.

*Index Terms*—Defocus, etch, lithography, placement, subresolution assist feature (SRAF).

#### I. INTRODUCTION

CROSS-CHIP linewidth variation induced by photolithography and etch processes has been a major barrier in ultradeep submicrometer manufacturing. Photolithography has been a key enabler of the aggressive IC technology scaling implicit in Moore's Law. Minimum feature sizes have outpaced the introduction of advanced lithography hardware solutions so that gate length and CD tolerances prescribed in the 2005 International Technology Roadmap for Semiconductors [2] are extremely difficult to achieve. As a result, resolutionenhancement techniques (RETs), such as optical proximity correction (OPC) [19], phase-shift masks [13], and off-axis illumination (OAI), are being pushed ever closer to fundamental resolution limits [6]. Combinations of these techniques can provide advantages for lithography manufacturing, e.g., OAI and OPC, together with subresolution assist features (SRAFs), achieve enhanced CD control, and focus margin at minimum pitch.

However, when OAI is used, there will always be pitches for which the angle of illumination works with the angle of diffraction to produce a bad distribution of diffraction orders in the lens. These pitches are called the forbidden pitches because of their lower printability, and designers should avoid such pitches in the layout. Forbidden pitches consist of horizontal (H) and vertical (V) forbidden pitches, depending on whether they are caused by interactions of poly geometries in the same cell row or in different cell rows, respectively. The resulting forbiddenpitch problem for the manufacturing-critical poly layer must be solved before detailed routing. Since the detailed routing works on a fixed placement, except on some small placement ECOs as required, it "locks in" the poly-layer layout. At the same time, we wish to address the forbidden-pitch problem as late as possible to avoid extra rework upon modification of the manufacturing recipe. We first describe a novel dynamicprogramming-based algorithm for Assist-Feature Correctness (AFCorr), which uses flexibility in detailed placement to avoid all possible H and V forbidden pitches and the manufacturing uncertainty that they cause.

Etch-dummy features are introduced into the layout to reduce the CD distortion induced by etch proximity. The etch dummies are placed outside of the active layers so that the leftmost and rightmost gates on active-layer regions are protected from ion scattering during the etch process. However, etch-dummy rules conflict with the SRAF insertion because each of the two techniques requires specific spacings from poly. In such a regime, the assist-feature-correct placement methodology must consider the assist-feature and etch-dummy corrections. In this paper, we also present a novel SRAF-aware etch-dummy insertion method (SAEDM) which applies flexible etch-dummy rules according to the distance from the active edge to the leftmost (or rightmost) poly. As a result, the layout will be more conducive to the assist-feature insertion after the etchdummy features have been inserted. Finally, we introduce a dynamic programming-based technique for Etch-dummy Correctness (EtchCorr) which can be combined with the SAEDM in detailed placement of standard-cell designs.

## A. Contributions of This Paper

In this paper, we present various analyses of lithographic printability within the context of the standard-cell-based design methodology. Our goal is to minimize CD variation and enhance feature printability and reliability. Our main contributions are as follows.

- We propose a novel post-detailed placement perturbation algorithm for AFCorr. The dynamic programming-based algorithm of AFCorr reduces the incidence of the forbidden pitches by calculating H and V perturbation costs and by finding an optimal perturbation of cell placements in a given row, subject to upper bounds on cell displacement. In particular, in conjunction with the intelligent processaware library layout, this technique can achieve substantial improvements in depth-of-focus (DOF) margin and CD control.

- We present a SAEDM which optimizes etch-dummy insertion to make the layout more conducive to the assistfeature insertion after the etch-dummy features have been inserted.

- 3) We describe the Corr post-detailed placement perturbation algorithm that combines the EtchCorr and AFCorr techniques, removes the forbidden pitches of resist CD, and reduces the skew between resist and etch CDs, all of which being done simultaneously. We test this method within a complete industrial flow and achieve up to 100% reduction in the number of cell border-poly geometries having forbidden-pitch violations.

- 4) Various techniques that combine AFCorr, SAEDM, and EtchCorr are validated with respect to wafer printability, database complexity, and device performance. The penalties in data size, OPC running time, and delay are within 3%, 4%, and 6%, respectively, which are negligible compared to the large printability improvements and to the inherent "noise" in the relevant place-and-route tools.

introduce a novel placement-perturbation technique for AFCorr. Evaluation flows to validate its impact on lithographic manufacturability and experimental results are described. In Section III, we describe the etch-dummy-insertion problems and the design-perturbation algorithms of SAEDM and EtchCorr for better etch-dummy insertion. Various techniques that combine AFCorr, SAEDM, and EtchCorr are evaluated with respect to printability and design metrics. We conclude in Section IV with directions for ongoing research.

# II. ASSIST-FEATURE CORRECTNESS

# A. RET and Layout Impact

The extension of optical lithography beyond the quartermicrometer regime has been enabled by a number of RETs. These RETs address the available three degrees of freedom in lithography, namely, aperture, phase, and/or pattern uniformity [16]. However, the adoption of different RETs dictates certain tradeoffs with various aspects of process and performance [3].

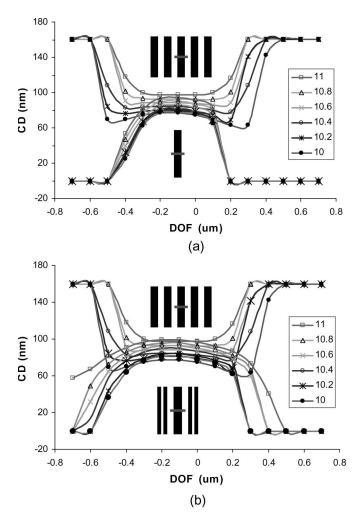

The OAI brings light to the mask at an oblique angle. As the angle of diffraction through certain aperture shapes matches a given pitch, higher order pattern information can be projected on the pupil plane as determined by the numerical aperture (NA) of the illumination system. This technique enables certain pitches on the mask to obtain higher resolution and extended focus margin. However, other pitches beyond the optimum angle will have a lower process margin compared with the conventional illumination (i.e., with a circular aperture). Since strong OAI is an essential technique in current lithography, these other pitches should be forbidden, and their avoidance is a new challenge for physical design automation. OPC is the deliberate and proactive distortion of photomask shapes to compensate for systematic and stable patterning inaccuracies. Bias OPC, the most common and straightforward application of OPC, has been proven to be a useful technique for matching photoresist edges to layout edges with essentially a layout sizing technique. However, bias OPC has limitations in enhancing process margins with respect to DOF and exposure dose. The Bossung plot<sup>1</sup> in Fig. 1 shows that the bias OPC is not sufficient to reduce the CD difference between isolated and dense patterns with varying focus and exposure dose. The CD distortion in the isolated pattern is usually a problem since lithography and RET recipes are not tuned or optimized for isolated lines [14]. The SRAF OPC technique combines pattern biasing with assist-feature insertion to compensate for the deficiencies of bias OPC. SRAFs [or scattering bars (SBs)], which are extremely narrow lines that do not actually print on the wafer, modify the wavefront and allow the lens pupil to receive higher order pattern information. The SRAFs are placed adjacent to primary patterns such that a relatively isolated primary line behaves more like a dense line. This works well for bringing the lithographic performance of the isolated and dense

# B. Organization of This Paper

The remainder of this paper is organized as follows. In Section II, we review RET and its layout impact, focusing our discussion on strong OAI and OPC with SRAF. We then

<sup>&</sup>lt;sup>1</sup>The Bossung plot shows multiple CDs versus defocus curves at different exposure doses and has been a useful tool to evaluate lithographic manufacturability. The common process window between the dense and isolated patterns is an increasingly important requirement to maintain CD tolerances in the subwavelength lithography regime.

Fig. 1. Comparison of Bossung plots between the dense and isolated lines. (a) Results of bias OPC. (b) Results of SRAF OPC.

lines into agreement. The DOF margin of the isolated line, as shown in Fig. 1(b), is considerably improved from that shown in Fig. 1(a), and a larger overlap of process window<sup>2</sup> between the dense and isolated lines is achieved.

The key observation is that the SRAF technique places more constraints on the spacing between patterns. The SRAFs can be added whenever a poly line is sufficiently isolated, but certain minimum assist-to-poly and assist-to-assist spacings are required to prevent SRAFs from printing in the space [12]. We now briefly review previous works related to forbidden pitches and their design implications. Socha et al. [18] observe that under more aggressive illumination schemes such as annular and quasar illuminations, some optical phenomena become more prominent, most notably the forbidden-pitch phenomenon. Shi et al. [17] give a theoretical analysis of pattern distortion in forbidden pitches due to the destructive light-field interference. Although SRAFs are an effective method to collect high-order diffraction on the entrance pupil plane of a projection lens [15], Shi et al. report that incorrect SRAF placements around a given main feature can actually degrade the process latitude of that feature. A number of previous works have proposed techniques

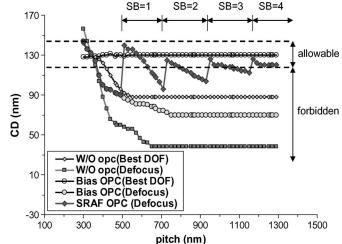

Fig. 2. Through pitch proximity plots for 130 nm technology: Best focus without OPC, worst defocus without OPC, worst defocus with BIAS OPC, and worst defocus with SRAF OPC are shown.

to control the forbidden pitches using optimization of optical conditions such as NA and illuminator aperture shape of OAI [11], [20], [21]. All of these works using optimizations of NA and OAI have sought to enlarge the ranges of allowable pitches, as shown in Fig. 2. However, approaches with process optimizations cannot completely remove the forbidden pitches, i.e., forbidden pitch always exists at any process conditions.

## B. SRAF Rule and Forbidden-Pitch Extraction

Lack of space may prohibit insertion of a sufficient number of SRAFs, and as a result, patterns may violate CD tolerance through defocus. Forbidden pitches are pitch values for which the tolerance of a given target CD is violated. Allowable pitches are all pitches other than the forbidden pitches. In this section, we summarize the criteria for SRAF insertion and forbiddenpitch extraction considering a worst defocus model. Our SRAF insertion rule is initially generated based on the theoretical background given in [17]. Positioning of SRAFs is then adjusted based on OPC results. Large CD degradation through pitch increases pattern bias as model-based OPC is applied, and this requires trimming of the SRAF rule to guarantee a better process margin and prevent the SRAFs from printing.<sup>3</sup> After applying SRAF OPC to test patterns with the best focus model, OPCed pitch patterns are simulated with the worst defocus model which will be described in detail in Section II-D. This evaluation yields the forbidden pitches, considering a maximum printability and manufacturability. The forbidden pitch rule is determined based on CD tolerance and worst defocus level, which are, in turn, dependent on the requirements of device performance and yield. The SRAF OPC restores printing when there is enough room for one SB. However, larger pitches are forbidden until there is enough room for two SBs. We thus can extract a set of forbidden pitches which will be demonstrated

<sup>&</sup>lt;sup>2</sup>Process window is defined as the range of exposure dose and defocus within which acceptable CD tolerance is maintained.

<sup>&</sup>lt;sup>3</sup>More complicated approaches to SRAF rule generation may involve cooptimization of model-based OPC and SRAF insertion. We do not address such involved optimizations of OPC since the focus of this paper is OPC-aware design and not OPC itself.

|       |       | 130 nm Lithogra     | aphy  | 90 nm Lithography   |       |  |  |  |

|-------|-------|---------------------|-------|---------------------|-------|--|--|--|

|       |       | $Pitch(X : \mu m)$  | Slope | $Pitch(X : \mu m)$  | Slope |  |  |  |

| #SRAF | f = 0 | $0 \le X < 0.51$    | 0:28  | $0 \le X < 0.41$    | 0:162 |  |  |  |

| #SRAF | i = 1 | $0:51 \le X < 0:73$ | 0:22  | $0:41 \le X < 0:57$ | 0:075 |  |  |  |

| #SRAF | = 2   | $0:73 \le X < 0:95$ | 0:105 | $0:57 \le X < 0:73$ | 0:062 |  |  |  |

| #SRAF | = 3   | $0:95 \le X < 1:17$ | 0:07  | $0:73 \le X < 0:89$ | 0:050 |  |  |  |

| #SRAF | = 4   | $1:17 \leq X$       | 0:02  | $0.89 \leq X$       | 0:012 |  |  |  |

TABLE I

I

SRAF RULE TABLE IN 130 nm AND 90 nm LITHOGRAPHY

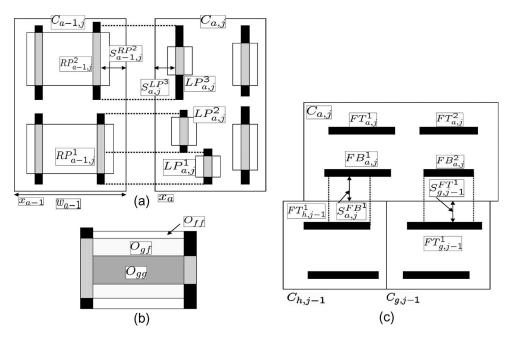

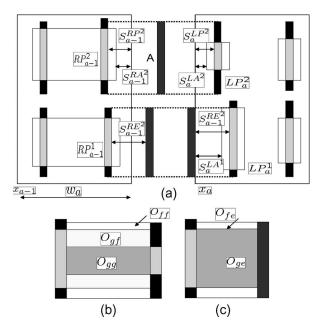

Fig. 3. (a) H interactions of gate-to-gate, gate-to-field, and field-to-gate polys. (b) Overlapped area in the region A of (a). (c) V interactions of field-to-field polys.

in Section II-D. In all of the works we report here, the CD tolerance is assumed to be  $\pm 10\%$  of minimum linewidth, whereas the worst defocus levels are assumed to be 0.5  $\mu$ m and 0.4  $\mu$ m for the 130 nm and 90 nm technology nodes, respectively. All of these results are summarized in Table I.

## C. AFCorr Placement Algorithm

In this section, we describe the proposed AFCorr placementperturbation algorithm for assist-feature correction. Single orientation polysilicon geometries are becoming common for the current and future process generations. We consider the H forbidden pitches within a cell row and the V forbidden pitches between adjacent cell rows [7], [8]. In this paper, we treat the placement of a given cell row independently of all other rows, even though the cost function is calculated with respect to both the H and V perturbations, in order to avoid all forbidden pitches. Assuming that the spacings within the cell are assist-correct, then the only source of incorrect spacings between poly shapes for the assist-feature insertion is cell placement. Adjacent cells within the same standard cell row. as well as cells within the adjacent cell rows that have shapes overlapping, interact for this purpose. The vertical poly shapes (typically gates) at the left and right peripheries of a cell, which overlap with similar shapes in the neighboring cells in the row, constitute the horizontal interaction. Similarly, horizontal poly shapes (typically field) at the top and bottom peripheries of the cell that overlap with the similar shapes in vertically adjacent cells (in adjacent rows) constitute the vertical interaction. In the following, we describe the single-row AFCorr perturbation algorithm, using which the 2-D AFCorr problem is solved one cell row at a time.

Let  $C_{a,j}$  be a cell at the  $a^{\text{th}}$  location in the  $j^{\text{th}}$  row. To explain the interactions of border-poly geometries, we adopt the following notations.

1) Horizontal polygon interaction: Given a cell  $C_{a,j}$ , let  $LP_{a,j}$  and  $RP_{a,j}$  be the sets of valid poly geometries in the cell, which are located closest to the left and right outlines of the cell, respectively. Only geometries with length that is larger than the minimum allowable length of SRAF features are considered. Define  $s_{a,j}^{\text{LP}^i}$  to be the space between the left outline of the cell and the *i*th left border-poly geometry.  $O_{\rm gg}$ ,  $O_{\rm ff}$ , and  $O_{\rm gf}$  correspond to the length of overlapped area in the cases of gate-to-gate, field-to-field, and gate-to-field polys, as shown in Fig. 3. In addition,  $c_{\rm gg}, c_{\rm ff}$ , and  $c_{\rm gf}$  are the proportionality factors which specify the relative importance of printability for gate and field polys.<sup>4</sup> Typically, gate poly geometries need to be better controlled through process as they have more direct impact on performance. Therefore, a typical order of importance is  $c_{gg} \ge c_{fg} \ge c_{ff}$ .

<sup>4</sup>Gate is the overlap region of polysilicon and diffusion. Field poly represents the rest area of polysilicon except for the gate.

2) Vertical polygon interaction: Given a cell  $C_{a,j}$ , let FB<sub>*a,j*</sub> and FT<sub>*a,j*</sub> be the sets of valid field poly geometries in the cell, which are located closest to the bottom and top outlines of the cell, respectively. Define  $s_{a,j}^{\text{FB}^{i}}(s_{a,j}^{\text{FT}^{i}})$  to be the space between the bottom (and top) outline of the cell and the *i*th bottom (and top) border-poly geometry.  $O_{\text{ff}}$  corresponds to the length of field-to-field overlap between the horizontal geometries in adjacent cell rows.<sup>5</sup>

Assume an ordered set  $AF = AF_1, \ldots, AF_m$  of spacings which are "assist-correct," i.e., if the spacing between the two gate poly shapes belongs to the set AF, then the required number of assist features can be inserted between the two poly geometries. For example, in Fig. 2, the peaks of the CD correspond to  $AF_i$ . The acceptable CD tolerance range (e.g., 10%) results in a range of acceptable pitches starting at  $AF_i$ . AF is assumed to be sorted in increasing order. Note that the set AF may contain a number of spacings which correspond to varying SRAF widths. Let  $w_a$  denote the width of cell  $C_{a,j}$ , and let  $x_a$  denote its (leftmost) placement coordinate in the given standard cell row, where coordinates increase from left to right. In addition, let  $\delta_{a,j}$  denote the placement perturbation of cell  $C_{a,j}$  to adjust the spacing between cells.  $\delta_{a,j}$  is positive if the cell is moved toward the right and negative otherwise. Then, the assist-correct placement perturbation problem is

- $\begin{array}{ll} \text{Minimize} & \sum |\delta_{a,j}| \\ \delta_{a,j} + x_{a,j} x_{a-1,j} \delta_{a-1} w_{a-1} + s_{a,j}^{\text{LP}^f} + s_{a-1,j}^{\text{RP}^g} \in \text{AF} \\ \text{s.t.} & \text{LP}^f \text{ and } \text{RP}^g \text{ overlap at the horizontal cell row} \\ & s_{a,j}^{\text{FB}^m} + s_{h,j-1}^{\text{FT}^n} \in \text{AF} \end{array}$

- s.t.  $FB^m$  and  $FT^n$  overlap at the vertical cell row. (1)

The objective can be made aware of cells in critical paths by a weighting function. Since the available number of allowable spacings is very small, obtaining a completely assistcorrect solution is usually not possible in a fixed cell-row width context. Therefore, a more tractable objective is to minimize the expected CD error at a predetermined defocus level. This "continuous" version of the problem is similar in nature to placement legalization of row-based placements but with manufacturability-based cost metrics instead of traditional wirelength metrics. Placement legalization has been previously solved in the literature [22] using dynamic programming techniques. We solve this "continuous" version of the aforementioned problem with the following dynamic programming recurrence:

$$Cost(1, b) = |x_1 - b|$$

$$Cost(a, b) = \lambda(a) |(x_a - b)| + Min_{i=x_{a-1}}^{x_{a-1}} + SRCH$$

$$\times \{Cost(a - 1, i) + \alpha HCost(a, b, a - 1, i)$$

$$+ \beta VCost(a, b)\}.$$

(2)

<sup>5</sup>Gates are typically laid out in a single orientation. We assume this orientation to be vertical in this paper.

| <b>HCost(a,b,a-1,i) of Cell</b> $C_{a,j}$                                                          |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Input:                                                                                             |  |  |  |  |  |  |  |

| User-defined weight for overlapping field polys : $c_{ff}$                                         |  |  |  |  |  |  |  |

| User-defined weight for overlapping gate polys : $c_{gg}$                                          |  |  |  |  |  |  |  |

| User-defined weight for overlapping gate and field polys : $c_{gf}$                                |  |  |  |  |  |  |  |

| Origin x (left) coordinate $C_{a,j} = b$                                                           |  |  |  |  |  |  |  |

| Origin x (left) coordinate $C_{a-1,j} = i$                                                         |  |  |  |  |  |  |  |

| Width of cell $C_{a,j} = w_a$                                                                      |  |  |  |  |  |  |  |

| Width of cell $C_{a-1,j} = w_{a-1}$                                                                |  |  |  |  |  |  |  |

| Output:                                                                                            |  |  |  |  |  |  |  |

| Value of $HCost(a, b, a-1, i)$ : horizontal cost of placing cell $C_a$                             |  |  |  |  |  |  |  |

| at placement site b when $C_{a-1}$ is placed at site i.                                            |  |  |  |  |  |  |  |

| Algorithm:                                                                                         |  |  |  |  |  |  |  |

| 01. <b>Case</b> $a = 1$ : $HCost(1, b, 0, i) = 0$                                                  |  |  |  |  |  |  |  |

| 02. <b>Case</b> $a > 1$ <b>Do</b>                                                                  |  |  |  |  |  |  |  |

| 03. For every pair of left poly geometry in cell $C_{a,j}(LP)$                                     |  |  |  |  |  |  |  |

| and right poly geometry in cell $C_{a-1,j}(RP)$ that overlap{                                      |  |  |  |  |  |  |  |

| 04. Call the geometries LP, RP                                                                     |  |  |  |  |  |  |  |

| /* Let Hspace be the spacing between LP and RP. Let $AF_l$ be                                      |  |  |  |  |  |  |  |

| the largest assist correct spacing smaller than Hspace. Let the CD                                 |  |  |  |  |  |  |  |

| degradation slope(delta CD/delta spacing) for $AF_l$ be $slope(l)$ . */                            |  |  |  |  |  |  |  |

| 05. Split the vertical overlap between LP and RP into field-to-field                               |  |  |  |  |  |  |  |

| $O_{ff}$ , field-to-gate $O_{fg}$ and gate-to-gate $O_{gg}$ overlaps.                              |  |  |  |  |  |  |  |

| /* Calculate overlap weight between RP and LP */                                                   |  |  |  |  |  |  |  |

| 06. weight = $slope(l) \times (Hspace - AF_l) \times (c_{ff}O_{ff} + c_{gf}O_{gf} + c_{gg}O_{gg})$ |  |  |  |  |  |  |  |

| s.t. $AF_{l+1} > Hspace \ge AF_l$ ,                                                                |  |  |  |  |  |  |  |

| 07. $HCost(a,b,a-1,i) \models weight$                                                              |  |  |  |  |  |  |  |

Fig. 4. Horizontal cost (HCost) calculation.

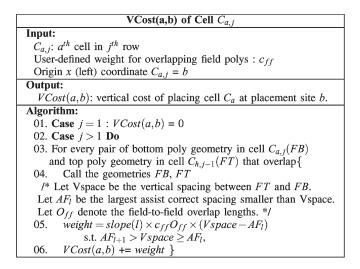

Cost (a, b) is the cost of placing cell a at placement site number b. The cells and the placement sites are indexed from left to right in the standard cell row.  $\alpha$  and  $\beta$  give the relative importance between HCost and VCost. Typically, HCost has more weight because HCost is related to gate printability which determines device performance. HCost is the measure of total expected CD degradation of vertical poly geometries at the worst defocus for the cell. It can be thought of as the weighted change in the area of vertical poly geometries in the cell. Similarly, VCost is the measure of total expected CD degradation of horizontal poly geometries at the worst defocus.

Note the aforementioned memoryless cost structure which ensures that once the optimal solution up to cell *i* is obtained, it contains the optimal solution up to cell i - 1. This optimal substructure is essential for dynamic programming. We restrict the perturbation of any cell to  $\pm$ SRCH placement sites from its initial location. This helps contain the delay and runtime overheads of AFCorr placement postprocessing.  $\lambda$  is a factor which decides the relative importance of preserving the initial placement and the final AFCorr benefit achieved for each given cell instance; in the current implementation,  $\lambda$  is directly proportional to the number of critical timing paths that pass through the given cell instance. HCost and VCost correspond to the printability deterioration under defocus conditions for the horizontal and vertical interactions, respectively. Cost (a, b)depends on the difference between the current nearest neighbor spacing of the polys and the closest assist-feature-correct spacing. The methods that we use to compute HCost and VCost are shown in Figs. 4 and 5. slope(l) is defined as the delta CD difference over delta pitch between  $AF_l$  and  $AF_{l+1}$ . Thus, perturbation cost is a function of slope, length, and weight of overlapped polys, and space for SRAF insertion. Our algorithm takes a legal placement as an input, and it outputs a legal placement with better DOF properties. In addition, VCost depends on the number of abutted cells L and R and the number of

Fig. 5. Vertical cost (VCost) calculation.

Fig. 6. (a) Cell placement before the horizontal AFCorr. (b) Cell placement after the horizontal AFCorr.

field-to-field poly interactions. The runtime of the AFCorr algorithm is  $O(\text{ncell} \times \text{SRCH})$ , where ncell is the total number of cells in the design.

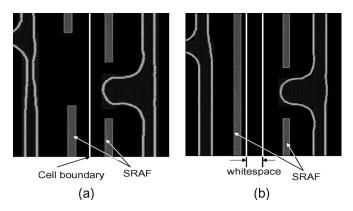

Fig. 6 shows an example of a resist image profile with and without AFCorr technique. The H forbidden pitch is caused by interactions of poly geometries in the same row. After cell-placement perturbation in horizontal direction, additional SRAFs can be inserted at increased whitespace between cells, and thus, pattern printability is enhanced. In addition, the V forbidden-pitch violation is caused by inter-cell row interactions. As shown in Fig. 7(a), there is not enough space between the vertically adjacent poly geometries (coming from cells in adjacent cell rows), which results in less SRAFs than needed. By moving the cell in the upper row leftward, this violation can be removed and the printability can be enhanced.

#### D. Experimental Setup and Results

We synthesize the aes and alu128 benchmark designs from Opencores in Artisan TSMC 130 nm and 90 nm libraries using the Synopsys Design Compiler v2003.06-SP1. aes synthesizes to 12 993 and 10 286 cells in 130 nm and 90 nm technologies, respectively. alu128 synthesizes to 13 279 and 8722 cells in 130 nm and 90 nm technologies, respectively. The synthesized

Fig. 7. (a) Cell placement before the vertical AFCorr. (b) Cell placement after the vertical AFCorr.

Fig. 8. Through pitch proximity plots and etch skew for 90 nm technology: Worst defocus with SRAF OPC and worst defocus with (left *y*-axis) etch OPC and (right *y*-axis) etch bias are shown.

netlists are placed with row utilization ranging from 50% to 90% using the Cadence First Encounter v3.3. All designs are trial-routed before running the timing analysis. On the lithography side, we use KLA-Tencor Prolith v9.1 to generate models for the OPC. Mentor Graphics Calibre v9.3\_5.12 is used for the model-based OPC, SRAF OPC, and optical rule checking. Photo simulation is performed with wavelength  $\lambda = 248$  nm and NA = 0.6 for 130 nm and  $\lambda = 193$  nm and NA = 0.75 for 90 nm. An annular aperture with  $\sigma = 0.85/0.65$  is used.

We use three printability quality metrics. Forbidden-pitch count is the number of border-poly geometries estimated as having greater than 10% CD error through-focus. Edge placement error (EPE) count is the number of edge fragments on border-poly geometries having greater than 10% EPE at the worst defocus level. SB count is the total number of SBs or SRAFs inserted in the design. A higher number of SRAFs indicates less through-focus variation and is hence desirable. We use  $c_{\rm fg} = c_{\rm gg} = c_{\rm ff} = 0.33$ ,  $\lambda(a) = {\rm sitewidth}/10 \times {\rm (number of top 200 critical paths passing through cell a)}$  and SRCH = 20.

|        |                  | 0               | 0     |       | 0     |       |       |       | 0     | -     | 0     |

|--------|------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        | Utilization (%): | ization (%): 90 |       | 8     | 80    |       | 70    |       | 60    |       | 0     |

|        | H:V weight       | H F/P           | V F/P | H F/P | V F/P | H F/P | V F/P | H F/P | V F/P | H F/P | V F/P |

| 130 nm | 0.9:0.1          | 4002            | 92    | 290   | 21    | 2     | 5     | 0     | 0     | 0     | 0     |

|        | 0.7:0.3          | 5234            | 60    | 533   | 15    | 5     | 2     | 1     | 0     | 0     | 0     |

|        | 0.5:0.5          | 5878            | 54    | 573   | 14    | 10    | 1     | 2     | 0     | 0     | 0     |

| 90 nm  | 0.9:0.1          | 4639            | 82    | 541   | 21    | 10    | 5     | 0     | 0     | 0     | 0     |

|        | 0.7:0.3          | 5321            | 70    | 721   | 15    | 11    | 2     | 1     | 0     | 0     | 0     |

|        | 0.5:0.5          | 6072            | 43    | 891   | 14    | 14    | 1     | 1     | 0     | 0     | 0     |

TABLE II SUMMARY OF FORBIDDEN-PITCH RESULTS. FORBIDDEN-PITCH COUNTS SLIGHTLY CHANGE BASED ON DIFFERENT H VERSUS V WEIGHTS

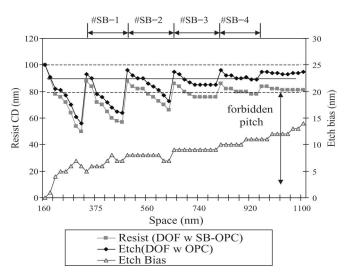

We first evaluate lithography printability of AFCorr with H and V assist corrections. Proximity plot with fixed linewidth for the 130 nm RET is shown in Fig. 2. CD degradation increases through pitch as the defocus level increases. Patterns in the pitches of over 0.4  $\mu$ m before an OPC are outside the allowable tolerance range at the worst defocus of 0.5  $\mu$ m. After the bias OPC, pitches up to 0.38  $\mu$ m are allowable for CD tolerance, whereas all pitches larger than 0.38  $\mu$ m should be forbidden. After evaluating the SRAF OPC patterns with the worst defocus model, a set of forbidden pitches of 0.13  $\mu$ m technique is obtained: [0.37, 0.51), [0.635, 0.73), [0.82, 0.95), and [1.09, 1.17) (in micrometers). The forbidden pitches still remain after SRAF OPC even though the SRAF insertion considerably reduces the forbidden pitches compared with the bias OPC. Proximity plot with SRAF OPC for 90 nm technology is shown in Fig. 8. Resist CDs after SRAF OPC are evaluated with the worst defocus model of 0.4  $\mu$ m. Resist CDs violate the allowable CD tolerance<sup>6</sup> as distance between the SRAF and the poly increases. A set of forbidden pitches of resist CD for 90 nm RET is calculated: [0.3, 0.41), [0.45, 0.57), [0.64, 0.73), and [0.78, 0.89) (in micrometers). We generated the SRAF rules which may be summarized, as shown in Table I. SRAF width and SRAF-to-pattern space are 40 nm and 120 nm, respectively, for 90 nm technology.

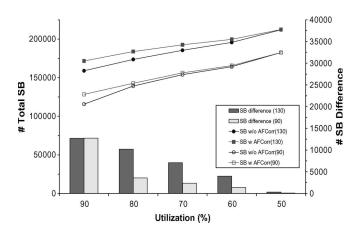

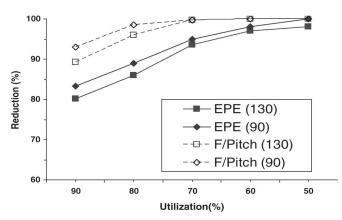

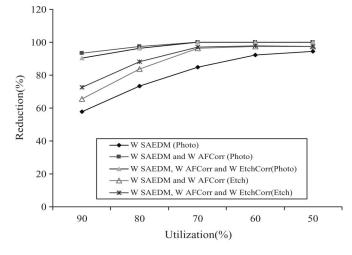

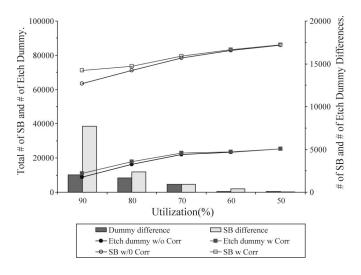

Table II shows the results of H and V forbidden pitches with various H versus V weights. Increasing weight of HCost reduces the number of H forbidden pitches while increasing the number of V forbidden pitches. H and V forbidden-pitch counts are reduced by 94%–100% and 76%–100% for 130 nm and by 96%-100% and 87%-100% for 90 nm, respectively. The design with 0.9  $\alpha$  for HCost and 0.1  $\beta$  for VCost weights results in the highest reductions of total forbidden-pitch counts and is chosen to evaluate the SB count, the running time, etc. Fig. 9 shows that the total number of SRAFs increases as the utilization decreases due to an increased whitespace between cells. The benefit of AFCorr decreases with lower utilization because the design has already enough whitespace for the SRAF insertion. Due to the additional number of SRAFs inserted, there is a small increase in SRAF OPC runtime (< 3.6%) and final data volume (< 3%). Reductions of EPE and forbidden pitch are investigated for each utilization, as shown in Fig. 10. Total forbidden-pitch count is reduced by 89%-100% in 130 nm and 93%-100% in 90 nm. The EPE count is reduced by 80%-98% in 130 nm and 83%-100% in 90 nm. In addition, the SB count improves by 0.1%-7.4% for 130 nm and 0%-7.9% for 90 nm.

Fig. 9. Number of SRAFs with and without AFCorr for each of the five different utilizations.

Fig. 10. Reductions of forbidden pitches with AFCorr methodology for each of the five different utilizations.

Note that these numbers are small as they correspond to the entire layout rather than just the border-poly geometries. The change in estimated post-trial route circuit delay ranges from -7% to +11%. All of these results for AFCorr are summarized in Table III.

## **III. ETCH-DUMMY CORRECTNESS**

# A. Etch Dummy and Layout Impact

Insertion of etch-dummy features has been introduced to reduce the CD difference between the resist and etch processes for 90 nm and below technology nodes. In dry etch processes such as plasma, ion, and reactive-ion etch, different consumptions of etchants with different pattern densities lead to etch skew between the dense and isolated patterns. For example, all available etchants in areas with low density are consumed

<sup>&</sup>lt;sup>6</sup>Allowable CD tolerance is assumed to be 10% of minimum linewidth in the worst defocus level.

TABLE III SUMMARY OF AFCorr RESULTS. RUNTIME DENOTES THE RUNTIME OF SRAF AND ETCH-DUMMY INSERTION AND MODEL-BASED OPC. THE AFCorr PERTURBATION RUNTIME RANGES FROM 2 TO 3 min FOR ALL TEST CASES, GDS SIZE IS THE POST-SRAF OPC DATA VOLUME

|        | Utilization (%): | 9       | 0      | 8       | 30     | 7       | 0      | 6       | 0      | 5       | 50     |

|--------|------------------|---------|--------|---------|--------|---------|--------|---------|--------|---------|--------|

|        | Flow:            | Typical | AFCorr |

| 130 nm | # Forbidden      | 20632   | 4094   | 3201    | 311    | 2011    | 7      | 1421    | 0      | 219     | 0      |

|        | # SB             | 158987  | 171691 | 173673  | 183860 | 185493  | 192578 | 195741  | 199704 | 212079  | 212412 |

|        | # EPE            | 4630    | 4721   | 5975    | 562    | 4276    | 15     | 1732    | 0      | 199     | 0      |

|        | Runtime (s)      | 7821    | 7902   | 7876    | 7934   | 7913    | 7973   | 7998    | 8013   | 8021    | 8121   |

|        | GDS (MB)         | 48.9    | 48.9   | 48.8    | 48.9   | 48.2    | 48.4   | 48.3    | 48.5   | 48.2    | 48.4   |

|        | Delay (ns)       | 4.2     | 4.6    | 4.5     | 4.7    | 4.5     | 4.6    | 4.6     | 4.9    | 5.2     | 5.4    |

| 90 nm  | # Forbidden      | 22121   | 4721   | 4821    | 562    | 3812    | 15     | 2001    | 0      | 321     | 0      |

|        | # SB             | 115652  | 128387 | 139182  | 147520 | 153904  | 156244 | 164264  | 165649 | 182572  | 182666 |

|        | # EPE            | 7523    | 1262   | 4813    | 532    | 2131    | 107    | 1329    | 59     | 163     | 5      |

|        | Runtime (s)      | 6211    | 6327   | 6322    | 6431   | 6482    | 6499   | 6521    | 6571   | 6672    | 6692   |

|        | GDS (MB)         | 43.1    | 43.3   | 43.2    | 43.3   | 43.2    | 43.3   | 43.7    | 43.8   | 44.6    | 44.8   |

|        | Delay (ns)       | 2.7     | 2.7    | 2.6     | 2.6    | 2.4     | 2.47   | 2.8     | 2.9    | 3.1     | 3.2    |

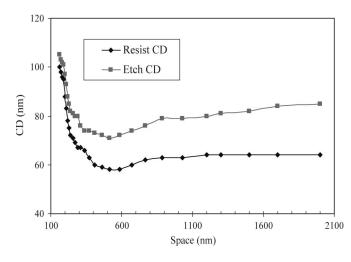

Fig. 11. Different proximity behaviors between photo and etching processes with pitch.

rapidly, and thus, the etch rate then drops off significantly. In areas with high density of patterns, the etchants are not consumed as quickly. As a result, the proximity behavior of the photo process differs from that of etch process, as shown in Fig. 11. Therefore, there is a CD skew between the resist and etch processes with varying pitch. In general, the etch skew of the two processes increases as the pitch increases. The OPC cannot determine the extent of layout distortion to match the layout pattern to the photoresist edges and the poly edge (after etch process) simultaneously. The OPC is typically used to compensate for the CD variation of the resist process, and then, the etch dummies are inserted to reduce the CD skew between the two processes.

When the etch dummies are placed adjacent to primary patterns, a relatively isolated primary line will behave more like a dense line, and thus, the etch dummies can reduce the etch skew. Moreover, the maximum relevant pitch is reduced through the etch-dummy insertion. This is an important consideration with respect to the model-based OPC, which calculates the proximity effect of all patterns within a given proximity range, such that a larger proximity range increases the OPC runtime. Granik [4] observes that the proximity range of the etch process is around 3  $\mu$ m, which prevents the conventional model-based OPC from delivering a good OPC mask within a feasible turnaround time.

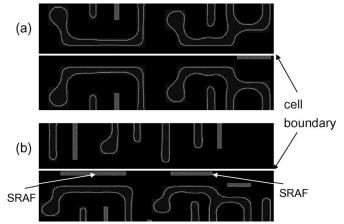

Fig. 12. Conflict between SRAF and etch-dummy rules. (a) Assist-feature missing. (b) Forbidden-pitch occurrence.

Fig. 13. (a) Typical etch-dummy generation. (b) SRAF-aware etch-dummy generation.

1) Etch-dummy-insertion problem: Given a layout, find an etch-dummy placement such that the following conditions are satisfied.

- Condition 1) Etch dummies are inserted between the primary patterns with certain spacing to reduce the etch skew between the resist and etch processes.

- Condition 2) Etch dummies are placed outside of the activelayer regions.

$\mathbf{S}$

TABLE IV Comparison of Etch-Dummy Rules Between the Conventional Etch-Dummy Method and the SAEDM. Note That  $AS_1 + AS_r = ES - ED_1$

| Etch    | dummy rules         | Typical       | method      | SAEDM        |              |  |

|---------|---------------------|---------------|-------------|--------------|--------------|--|

|         | $ES(\mathbf{X})$    | $DS_l$ $DS_r$ |             | $DS_l$       | $DS_r$       |  |

| #ED = 0 | $0 \le X < ED_1$    |               |             |              |              |  |

| #ED = 1 | $ED_1 \le X < ED_2$ | (ES - EW)/2   | (ES - EW)/2 | $AS_l + DAS$ | $AS_r + DAS$ |  |

| #ED = 2 | $X \leq ED_2$       | DAS           | DAS         | $AS_l + DAS$ | $AS_r + DAS$ |  |

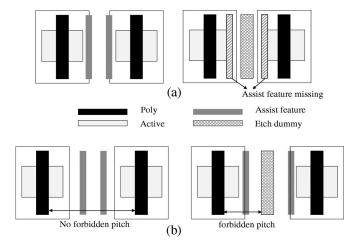

Thus, the etch-dummy-correction problem is used to determine perturbations to intercell spacings to maximize insertion of etch dummy. Forbidden-pitch correction in the resist process is required after inserting the etch dummy because the etch dummy cannot be placed too close to the primary patterns due to Condition 2). The etch-dummy insertion can make the printability of the resist process worse in certain pattern configurations. Fig. 12 shows examples such as (a) missing assist feature and (b) forbidden-pitch occurrence. The assist features can be missed due to the lack of space between the primary pattern and the etch dummy even when there is enough space to insert multiple SRAFs before the etchdummy insertion. New forbidden pitches for assist features can occur in the spacing between the poly and the etch dummy due to the mismatch between the rules for assist-feature and etch-dummy corrections. Therefore, we now propose a new Corr problem that combines the assist-feature and etch-dummy insertion methods as follows.

Assist-feature- and etch-dummy-correction problem: Given a standard-cell layout, determine the perturbations to intercell spacings to simultaneously insert the SRAFs in forbidden pitches and insert the etch dummies to reduce the etch skew.

## B. SRAF-Aware Etch-Dummy Generation

To reduce the etch proximity, at most one etch dummy for each active (or diffusion) geometry is needed since the etch skew depends on pattern-to-pattern spacing regardless of local pattern density [10], i.e., the etch skew decreases as the spacing is reduced. SRAFs and etch dummies have been generated by rule-based methods with lookup tables since the simulation tools are much slower than the rule-based tools. Typically, etchdummy rules consist of etch dummy-to-active space (DAS), etch-dummy width (EW), and etch dummy-to-dummy space (DDS) with respective values of 120, 100, and 200 nm being typical for 90 nm technology. Let ES denote the space between the active geometry in the left and right cells, as shown in Fig. 13. Let  $ED_1$  and  $ED_2$  denote the required spaces to insert one and two etch dummies in ES, respectively. For typical methods of etch-dummy insertion, the minimum space rules for one and two etch dummies are  $ED_1 = 2 * DAS + EW$  and  $ED_2 = 2 * DAS + 2 * EW + DDS$ , respectively. The first etch dummy in the typical etch-dummy rule is always placed at the center of the space between the two active geometries, whereas the active-to-etch-dummy space for the second etch dummy is always according to the space rule (DAS).

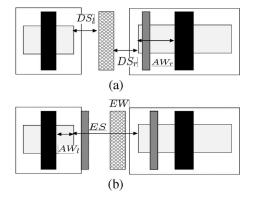

Once the etch dummies have been inserted for only etchproximity control, the spacing between the poly and the etch dummy may not be appropriate for the SRAF insertion. Fig. 13(a) shows an example where the left-hand-side SRAF cannot be inserted due to the lack of poly-to-etch-dummy spacing. Let AW<sub>1</sub> and AW<sub>r</sub> denote the distances between the border polys and the active geometries located at the left and right cells, respectively. Let  $AF = AF_1, \ldots, AF_m$  denote a set of "assist-correct" spacings.  $AF_j$  is the  $j^{\text{th}}$  member of the set of assist-feature-correct spacings AF. Let AS<sub>1</sub> and AS<sub>r</sub> denote the additional spacings needed for assist-correctness in the left and right cells, respectively. To avoid missing SRAFs and occurrence of forbidden pitches, we propose a new SAEDM considering active width (AW) during the insertion of etch dummy, as follows:

Minimize index values of j and k in a set AF

t.

$$AS_{l} = AF_{j} - (AW_{l} + DAS)$$

$$AS_{r} = AF_{k} - (AW_{r} + DAS)$$

$$(AS_{l} + AS_{r}) \le (ES - ED_{1}).$$

(3)

The SAEDM searches assist-correct spacings with minimum index values in a set AF, so that the sum of the additional spacings  $AS_1$  and  $AS_r$  corresponding to the assist-correct spacings is less than (ES – ED<sub>1</sub>). Let DS<sub>1</sub> and DS<sub>r</sub> denote the left and right spaces from the etch dummy to the border active geometries in the left and right cells, respectively. Thus, new etch-dummy spaces of DS<sub>1</sub> =  $AS_1$  + DAS and DS<sub>r</sub> =  $AS_r$  + DAS are both assist-correct and etch-dummy correct. Note that the etch dummy after SAEDM is no longer located at the center of an active-to-active space since DS<sub>1</sub> differs from DS<sub>r</sub>, as shown in Fig. 13(b). Table IV compares the DS<sub>1</sub> and DS<sub>r</sub> values returned by the typical etch-dummy method and by the SAEDM.

## C. Corr Placement Algorithm

Assist-correct pitch rules are violated if there is not enough space to insert  $AS_1$  and  $AS_r$ . We now describe an etch-dummycorrection placement-perturbation algorithm that uses intelligent whitespace management. EtchCorr differs from AFCorr as follows: 1) Corr is based on the active-to-cell outline spacing, whereas AFCorr is based on the poly-to-cell outline spacing; and 2) Corr calculates the virtual positions of etch dummy in order to both insert the SRAF in assist-correct spacing and the etch dummy in etch-dummy-correct spacing (EDS). Let EDS be the interdevice spacing with etch skew less than 10% of minimum linewidth. Thus, the etch-dummy-correct perturbation problem is used to minimize design perturbation to insert the etch dummies optimally and, thus, to reduce the etch skew between the resist and etch processes. However, as discussed above, a new design correction technique Corr which combines the assist-correct (AFCorr) and etch-correct (EtchCorr) placement methods is required to avoid conflict between the assist-feature and etch-dummy insertions.

Fig. 14. Placement-perturbation problem for assist and etch-dummy insertion. (a) Multiple interactions of gate-to-dummy and field-to-dummy. (b) Overlap area when there is no etch dummy. (c) Overlap area in the presence of etch dummy.

In the following, we describe the single-row Corr perturbation algorithm. Let  $s_a^{\text{RP}_i}$  and  $s_a^{\text{RA}_j}$  denote the spacing between the right outline of the cell and the *i*<sup>th</sup> right borderpoly, and the spacing between the right outline of the cell and the *j*<sup>th</sup> active geometry, respectively.  $s_a^{\text{RE}_i}$  is the spacing from the right border-poly to the etch dummy, as shown in Fig. 14. Let  $\delta$  denote a cell-placement perturbation to adjust the spacing between cells. ES, the space between border actives, is  $x_a - x_{a-1} - w_{a-1} + s_{a-1}^{\text{RA}_i} + s_a^{\text{LA}_i}$ . Then, the **Corr placement-perturbation problem** is

$$\begin{array}{l} \text{Minimize } \sum |\delta_i| \text{ such that} \\ \begin{cases} \text{If } (\text{ES} < \text{ED}_1) \\ \delta_a + x_a - x_{a-1} - \delta_{a-1} - w_{a-1} + s_{a-1}^{\text{RP}^i} + s_a^{\text{LP}^i} \in \text{AF} \\ \delta_a + x_a - x_{a-1} - \delta_{a-1} - w_{a-1} + s_{a-1}^{\text{RA}^i} + s_a^{\text{LA}^i} \in \text{EDS} \\ \text{s.t.} - \text{SRCH} \le \delta_{a-1} \text{ and } \delta_a \le \text{SRCH} \\ \text{otherwise} \\ S_{a-1}^{\text{RP}^i} - S_{a-1}^{\text{RA}^i} + S_{a-1}^{\text{RE}^i} + \delta_{a-1}, S_a^{\text{LP}^i} - S_a^{\text{LA}^i} + S_a^{\text{LE}^i} + \delta_a \in \text{AF} \\ S_{a-1}^{\text{RE}^i} + \delta_{a-1} \text{ and } S_a^{\text{LE}^i} + \delta_a \in \text{EDS} \\ \text{s.t.} - \text{SRCH} \le \delta_{a-1} \text{ and } \delta_a \le \text{SRCH} \end{cases}$$

$$Cost(1, b) = |x_1 - b|$$

$$Cost(a, b) = \lambda(a)|(x_a - b)| + Min_{i=x_{a-1}-SRCH}^{x_{a-1}+SRCH} \times \{Cost(a - 1, i) + W_1AFCost(a, b, a - 1, i) + W_2EDCost(a, b, a - 1, i)\}.$$

(5)

The terms AFCost and EDCost denote the assist-feature and etch-dummy costs, respectively. AFCost depends on the

Fig. 15. Algorithm for AFCost and EDCost computations.

Fig. 16. Modified design and evaluation flows: Note the added steps of forbidden-pitch extraction, SAEDM, and post-placement optimization to the ASIC design flow.

difference between the current nearest neighbor spacing of the polys and the closest assist-correct spacing. The methods of computing AFCost and EDCost are shown in Fig. 15.<sup>7</sup> The formulation is similar to the AFCorr when the space

<sup>&</sup>lt;sup>7</sup>The figure shows only the horizontal AFCost computation for simplicity. We do not compute the vertical EDCost as the primary focus of the etch-dummy gate CD control.

| Stage | Etch time | Material     | Vertical etch | Horizontal etch | Faceting Parameter |

|-------|-----------|--------------|---------------|-----------------|--------------------|

|       | (sec)     |              | rate (sec)    | rate (sec)      | Parameter          |

| 1     | 10        | ArF Sumitomo | 10.66         | -0.6            | 0.5                |

|       |           | AZ BarLi-2   | 10.52         | -0.7            | 0.0                |

|       |           | Si Nitride   | 10.28         | -0.7            | 0.0                |

| 2     | 60        | ArF Sumitomo | 0.3           | -0.12           | 0.5                |

|       |           | AZ BarLi-2   | 3.4           | -0.2            | 0.0                |

|       |           | Si Nitride   | 30.4          | -0.3            | 0.0                |

| 3     | 36        | ArF Sumitomo | 10.65         | 0.9             | 0.5                |

|       |           | AZ BarLi-2   | 0.25          | 1.0             | 0.0                |

|       |           | Si Nitride   | 0.0           | 1.5             | 0.0                |

TABLE

V

ETCH-PROCESS CONDITIONS FOR THE SIMULATOR IN 90 nm TECHNIQUE

between the border actives is not enough for a dummy insertion. However, the Corr perturbation problem calculates the poly-to-dummy spacings instead of the poly-to-poly spacings when there are etch dummies between cells.  $O_{\rm gg}$ ,  $O_{\rm ff}$ , and  $O_{\rm ff}$  correspond to the length of overlap areas of gate-to-gate, field-to-field, and gate-to-field polys, respectively, as shown in Fig. 14.  $O_{\rm ge}$  and  $O_{\rm fe}$  correspond to the overlapped length of gate-to-dummy and field-to-dummy, respectively. In addition,  $c_{\rm gg}$ ,  $c_{\rm ff}$ , and  $c_{\rm ff}$  are the proportionality factors which specify the relative importance of printability for gate and field polys.  $W_1$  and  $W_2$  are user-defined weights for AFCost and EDCost, respectively.

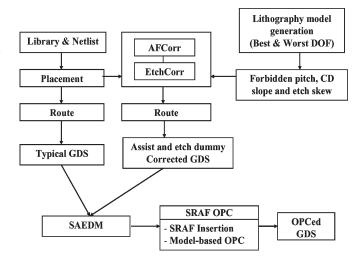

## D. Modified Design and Evaluation Flow

To account for new geometric constraints that arise due to SRAF OPC in physical design, we add forbidden-pitch extraction and postplacement optimization into the current application-specific integrated-circuit (ASIC) design methodology. Fig. 16 shows the modified design and evaluation flows in the regime of forbidden-pitch restrictions. Of course, we must assume that the library cells themselves have been laid out with awareness of forbidden pitches, and indeed, our experiments with commercial libraries confirm that there are no forbidden-pitch violations in poly geometries within individual commercial standard cells. Our method solves the forbiddenpitch violations between the placed cells. The SRAF insertion rules of enhancing the DOF margin are determined based on the best and worst focus models.<sup>8</sup>

The post-placement optimization is performed based on the forbidden pitches and the slopes of CD error within them. After AFCorr (SAEDM and EtchCorr techniques will be described next in detail in this section), we obtain a new placement which is more conducive to the insertion of SRAFs, thus allowing a larger process window to be achieved. The two layouts generated by the conventional and assist-correct flows undergo a comprehensive SRAF OPC. The amount and impact of the applied RET are functions of the circuit layout. Thus, we can evaluate how the assist-correct placement impacts circuit performance and printability/manufacturability according to the metrics of SRAF insertions and EPE. The following sections give more details of forbidden-pitch extraction and design implementation.

## E. Experimental Setup and Results

To account for new geometric constraints that arise due to SRAF and etch dummy in physical design, we extract the forbidden pitch, the CD slopes of the resist and etch processes with pitch, and the CD skew induced by the etch process. Postplacement optimization generates a new placement wherein the coordinates of cells have been adjusted to avoid the forbidden pitches and to reduce the etch skew. The target etch process consists of three etch steps: 10-s breakthrough etch step to get through the bottom anti-reflective coating, 60-s main etch step, and 36-s overetch step. The breakthrough and main etch steps in the model produce a fair amount of deposition, taking the resist profile to 100 nm. The overetch step trims this back to the 90 nm range. A set of etch parameters is shown in Table V. We only consider the first etch step to remove the Si nitride because the second etch step, a step to etch the gate poly, does not impact the CD variation with pitch [1].

We use the same benchmark designs as AFCorr and evaluate the pattern printability with combinations of the following: 1) SAEDM; 2) AFCORR+SAEDM; and 3) AFCorr+ EtchCorr+SAEDM. We generated the SRAF rules with results in Table I. SRAF width and SRAF-to-pattern space are 40 and 120 nm, respectively. In addition, DAS, EW, and etch DDS correspond to 120, 100, and 200 nm, respectively. However, the spacing between active and etch dummy is varying because the SAEDM changes the space with the AW. The resist and etch CDs vary with location of the SRAF insertion, and the resist CDs violate the allowable CD tolerance as distance between the SRAF and the poly increases. The trend of etch CD follows the variation of resist CD. The skew of resist and etch CDs continuously increases with pitch and is not saturated by 1.1  $\mu$ m, as shown in Fig. 8.

After the Corr placement perturbation, we obtain a new placement wherein the coordinates of cells minimize the occurrence of forbidden pitches of the resist and etch processes. The total cost of Corr is calculated using the specific weights of the resist and etch costs (in the results reported, we use the respective weights  $W_1 = 0.9$  and  $W_2 = 0.1$ ). Note that our post-placement perturbation problem reduces to the previously studied AFCorr problem if  $W_2 = 0$ .

<sup>&</sup>lt;sup>8</sup>In general, the best focus is shifted from zero to about 0.1  $\mu$ m due to the refraction in the resist. The worst defocus is the maximum allowable defocus corner for manufacturability in a lithography system. As the CD tolerance is  $\pm 10\%$ , the worst defocus model can be extracted by the Bossung plot in Fig. 1, i.e., worst defocus model is 0.5  $\mu$ m for 130 nm technology.

TABLE

VI

Forbidden-Pitch Results With Various Etch-Dummy Insertion Methodologies in the Resist and Etch Processes

|       | Utilization (%):                        | 90    | 80    | 70    | 60    | 50    |

|-------|-----------------------------------------|-------|-------|-------|-------|-------|

| Photo | W/O SAEDM, W/O AFCorr, W/O EtchCorr     | 37433 | 31314 | 29216 | 26765 | 21282 |

|       | W SAEDM, W/O AFCorr, and W/O EtchCorr   | 15743 | 8330  | 4423  | 2075  | 1198  |

|       | W SAEDM, W AFCorr, and W/O EtchCorr     | 2432  | 822   | 23    | 0     | 0     |

|       | W SAEDM, W AFCorr, and W EtchCorr       | 3566  | 1116  | 51    | 0     | 0     |

| Etch  | W/O SAEDM, W/O AFCorr, and W/O EtchCorr | 15816 | 8812  | 4656  | 4345  | 3530  |

|       | W SAEDM, W/O AFCorr, and W/O EtchCorr   | 16418 | 9729  | 5282  | 5002  | 4209  |

|       | W SAEDM, W AFCorr, and W/O EtchCorr     | 5423  | 2221  | 172   | 109   | 92    |

|       | W SAEDM, W AFCorr, and W EtchCorr       | 4321  | 1032  | 143   | 92    | 92    |

Fig. 17. Reductions of forbidden pitches with various etch-dummy insertion methodologies for each of the five different utilizations.

Fig. 18. Numbers of inserted SRAF and etch-dummy features with various etch-dummy insertion methodologies for each of the five different utilizations.

We evaluate the reduction of forbidden-pitch count with various etch-dummy insertion methodologies in the resist and etch processes shown in Table VI. After 1) SAEDM, the forbiddenpitch count of photo process can be reduced by 57%–94% with various utilizations because the etch-dummy-to-poly spacings become assist-correct. However, the forbidden-pitch count of the etch process may increase by up to 6% in certain layout configurations since the SAEDM increases the poly-to-etchdummy spacing. The forbidden-pitch counts of etch process in 2) SEADM+AFCorr and 3) Corr+SAEDM are reduced by up to 64%–97% and 73%–98%, respectively, across a range of utilizations, as shown in Fig. 17. Corr+SAEDM facilitates additional SRAF and dummy insertions by up to 10.8% and 18.6%, respectively. Fig. 18 shows that the total numbers of SRAFs and etch dummies increase as the utilization decreases. Note that these numbers are small as they correspond to the entire layout rather than just the border-poly geometries. The EPE count is reduced by 91%-100% in the resist process and 72%-98% in the etch process. The change in the estimated post-trial route circuit delay ranges from 3% to 5.8%. The increases of data size and OPC running-time overheads of Corr are within 3% and 4%, respectively. The runtime of Corr placement perturbation is negligible ( $\sim 5 \text{ min}$ ) compared with the running time of OPC ( $\sim 2.5$  h). All of these results for Corr are summarized in Table VII.

## IV. CONCLUSION AND ONGOING WORK

In this paper, we have presented novel methods to optimize the etch-dummy insertion rules and the detailed standard-cell placements for improved etch-dummy and assist-feature insertions. We obtain a practical and effective approach to achieve assist-feature compatibility in physical layouts. AFCorr, as an approach to achieve the assist-feature compatibility, leads to reduced CD variation and enhanced DOF margin. We also introduce a dynamic programming-based technique (Corr) to achieve etch-dummy-insertion correctness in the detailed placement step of standard-cell-based chip implementation. Corr with SAEDM leads to reduced CD variation and increased insertion of assist features and etch dummies. For our test industrial cases, we have observed the following.

- In lithographic-printability evaluation of AFCorr, the H and V forbidden-pitch counts for border-poly geometries are reduced by 94%–100% and 76%–100% for 130 nm and by 96%–100% and 87%–100% for 90 nm, respectively. For EPE count, reductions of 80%–98% in 130 nm and 83%–100% in 90 nm are obtained. We also achieve up to 7.6% increase in the number of inserted SBs.

- In pattern-printability evaluation, the forbidden-pitch counts of photo process between the polysilicon shapes of neighboring cells are reduced by up to 54%–94%, 92%–100%, and 90%–100% for SAEDM, SAEDM+AFCorr, and SAEDM+Corr, respectively. The forbidden-pitch counts of etch process of SEADM+AFCorr and SAEDM+Corr are reduced by up

|       | Utilization(%): | 90      |            | 80      |            |         | 70         |         | 60         |         | 50         |

|-------|-----------------|---------|------------|---------|------------|---------|------------|---------|------------|---------|------------|

|       | Flow:           | Typical | SAEDM+Corr |

| Photo | # EPE           | 42102   | 3723       | 32434   | 1243       | 29349   | 98         | 28721   | 13         | 23134   | 2          |

|       | # Forbidden     | 37433   | 3566       | 31314   | 1116       | 29216   | 51         | 26765   | 0          | 21282   | 0          |

|       | # SB            | 63349   | 71051      | 71101   | 73501      | 78513   | 79432      | 82820   | 83230      | 85991   | 86026      |

| Etch  | # EPE           | 17209   | 4812       | 9213    | 1200       | 4820    | 182        | 4821    | 109        | 3890    | 109        |

|       | # Forbidden     | 15816   | 4321       | 8812    | 1032       | 4656    | 143        | 4345    | 92         | 3530    | 92         |

|       | # Dummy         | 8876    | 10911      | 16240   | 17920      | 22088   | 23001      | 23390   | 23499      | 25237   | 25309      |

| Other | Runtime (s)     | 6835    | 7011       | 7451    | 7535       | 7529    | 7632       | 7685    | 7698       | 7943    | 7944       |

|       | GDS (MB)        | 41.1    | 42.3       | 41.2    | 43.2       | 42.2    | 42.3       | 42.9    | 42.8       | 43.6    | 43.6       |

|       | Delay (ns)      | 2.478   | 2.305      | 2.458   | 2.602      | 2.522   | 2.47       | 2.867   | 3.176      | 3.113   | 3.046      |

TABLE VII SUMMARY OF SAEDM+Cort Results. Runtime Denotes the Runtime of SRAF and Etch-Dummy Insertions, as Well as the Model-Based OPC. The Cort Perturbation Runtime Ranges From 4 to 5 min for All Test Cases. GDS Size Is the Post-OPC Data Volume

to 64%–97% and 73%–98%, respectively, across a range of utilizations. Corr with SAEDM facilitates additional SRAF and dummy insertions by up to 10.8% and 18.6%, respectively.

3) In impact on other design metrics, the increases of data size, OPC running time, and maximum delay overheads of Corr are within 3%, 4%, and 6%, respectively. In addition, the maximum delay overhead of 6% is within noise of the P&R tools [5]. The runtime of Corr placement perturbation is negligible (~5 min) compared with the running time of OPC (~2.5 h).

We are currently engaged in further experimental validation and research. Certain devices and cells may be able to tolerate more process variations than others in the design. We are investigating techniques to bias the AFCorr and EtchCorr solutions in favor of such devices to reduce timing and power impact and to increase overall parametric yield.

#### REFERENCES

- [1] KLA-Tencor ProLith User's Manual.

- [2] International Technology Roadmap for Semiconductors, 2005. [Online]. Available: http://public.itrs.net

- [3] L. Capodieci, P. Gupta, A. B. Kahng, D. Sylvester, and J. Yang, "Toward a methodology for manufacturability driven design rule exploration," in *Proc. ACM/IEEE DAC*, Jun. 2004, pp. 311–316.

- [4] Y. Granik, "Correction for etch proximity: New models and applications," in *Proc. SPIE*, 2001, vol. 4346, pp. 98–112.

- [5] A. B. Kahng and S. Mantik, "Measurement of inherent noise in EDA tools," in *Proc. ISQED*, 2002, pp. 206–211.

[6] P. Gupta and A. B. Kahng, "Manufacturing-aware physical design," in

- [6] P. Gupta and A. B. Kahng, "Manufacturing-aware physical design," in *Proc. IEEE/ACM ICCAD*, Nov. 2003, pp. 681–687.

- [7] P. Gupta, A. B. Kahng, and C.-H. Park, "Detailed placement for improved depth of focus and CD control," in *Proc. Asia South Pacific Des. Autom. Conf.*, Jan. 2005, pp. 343–348.

- [8] P. Gupta, A. B. Kahng, and C.-H. Park, "Manufacturing-aware design methodology for assist feature correctness," in *Proc. SPIE*, Feb. 2005, pp. 131–140.

- [9] P. Gupta, A. B. Kahng, and C.-H. Park, "Enhanced resist and etch CD control by design perturbation," in *Proc. 25th BACUS Symp. Photomask Technol. Manage.*, Nov. 2005, vol. 5992, pp. 599 23P-1–599 23P-11.

- [10] K. Hashimoto, T. Kuji, S. Tokutome, T. Kotani, S. Tanaka, and S. Inoue, "A tandem process proximity correction method," in *Proc. SPIE*, 2002, vol. 4691, pp. 1070–1081.

- [11] K. Kim, Y. Choi, R. Socha, and D. Flagello, "Optimization of process condition to balance MEF and OPC for alternating PSM," in *Proc. SPIE*, 2002, vol. 4691, pp. 240–246.

- [12] L. W. Liebmann, "Layout impact of resolution enhancement techniques: Impediment or opportunity?" in *Proc. IEEE/ACM ISPD*, 2003, pp. 110-117.

- [13] M. Levenson, N. Viswanathan, and R. Sympson, "Improving resolution in photolithography with a phase-shifting mask," *IEEE Trans. Electron Devices*, vol. ED-29, no. 12, pp. 1812–1846, Dec. 1982.

- [14] C.-H. Park, Y.-H. Kim, J.-S. Park, K. Kim, M.-H. Yoo, and J.-T. Kong, "A systematic approach to correct critical patterns induced by the lithography process at the full-chip level," in *Proc. SPIE*, 1999, vol. 3679, pp. 622–700.

- [15] J. Petersen, "Analytical description of anti-scattering and scattering bar assist features," in *Proc. SPIE*, 2000, vol. 4000, pp. 77–89.

- [16] F. M. Schellenberg, L. Capodieci, and R. Socha, "Adoption of OPC and the impact on design and layout," in *Proc. IEEE/ACM DAC*, 2001, pp. 89–92.

- [17] X. Shi, S. Hsu, F. Chen, M. Hsu, R. Socha, and M. Dusa, "Understanding the forbidden pitch phenomenon and assist feature placement," in *Proc. SPIE*, 2002, vol. 4689, pp. 985–996.

- [18] R. Socha, M. Dusa, L. Capodieci, J. Finders, F. Chen, D. Flagello, and K. Cummings, "Forbidden pitches for 130 nm lithography and below," in *Proc. SPIE*, 2000, vol. 4000, pp. 1140–1155.

- [19] J. Stirniman and M. Rieger, "Fast proximity correction with zone sampling," in *Proc. SPIE*, 1994, vol. 2197, pp. 294–301.

- [20] A. Wong, R. Ferguson, S. Mansfield, A. Molless, D. Samuels, R. Schuster, and A. Thomas, "Level-specific lithography optimization for 1-Gb DRAM," *IEEE Trans. Semicond. Manuf.*, vol. 13, no. 1, pp. 76–87, Feb. 2000.

- [21] J. Word, S. Zhu, and J. Sturtevant, "Assist feature OPC implementation for the 130 nm technology node with KrF and no forbidden pitches," in *Proc. SPIE*, 2002, vol. 4691, pp. 1139–1147.

- [22] A. B. Kahng, I. Markov, and S. Reda, "On legalization of row-based placements," in *Proc. IEEE Great Lakes VLSI Symp.*, 2004, pp. 214–219.

**Puneet Gupta** (S'01–M'03) received the B.Sc. degree in electrical engineering from the Indian Institute of Technology Delhi, New Delhi, India, and the Ph.D. degree from the University of California, San Diego, La Jolla.

He is a Professor with the Department of Electrical Engineering, University of California, Los Angeles. He is also a Cofounder of Blaze DFM, Inc., Sunnyvale, CA. He has published more than 40 papers. He is the holder of one patent. His research interests include the design-manufacturing interface.

Dr. Gupta has previously copresented an embedded tutorial on Manufacturing Aware Physical Design at the International Conference on Computer Aided Design 2003 and instructed a short course at the SPIE Advanced Lithography 2007. He received the IBM Ph.D. Fellowship.

Andrew B. Kahng (SM'07) received the A.B. degree in applied mathematics (physics) from Harvard College, Cambridge, MA, and the M.S. and Ph.D. degrees in computer science from the University of California, San Diego (UCSD), La Jolla.

He joined the Computer Science Department, University of California, Los Angeles (UCLA), as an Assistant Professor in July 1989 and then became an Associate Professor in July 1994 and a Full Professor in July 1998. He has published more than 300 journal and conference papers. In January

2001, he became a Professor with the Computer Science and Engineering (CSE) Department and the Electrical and Computer Engineering (ECE) Department, UCSD, where he also served as an Associate Chair with the CSE Department, UCSD, from 2003 to 2004. He cofounded Blaze DFM, Inc., in October 2004, where he served as the Chief Technology Officer until resuming his duties at UCSD in September 2006. Since 1997, his research in IC design for manufacturability has pioneered methods for automated phase-shift mask layout, variability-aware analyses and optimizations, CMP fill synthesis, and parametric yield-driven cost-driven methodologies for chip implementation.

Prof. Kahng has been an Executive Committee Member of the MARCO Gigascale Systems Research Center since its inception in 1998. He has received NSF Research Initiation and Young Investigator awards, 11 Best Paper nominations, and six Best Paper awards. He was the founding General Chair of the 1997 ACM/IEEE International Symposium on Physical Design and cofounder of the ACM Workshop on System-Level Interconnect Prediction. He defined the physical design roadmap as a member of the Design Tools and Test Technology Working Group for the 1997, 1998, and 1999 renewals of the International Technology Roadmap for Semiconductors. From 2000 to 2003, he was the Chair of both the U.S. Design Technology Working Group and the Design International Technology Working Group (ITWG) and continues to serve as the Cochair of the Design ITWG.

**Chul-Hong Park** (S'03) received the B.S. and M.S. degrees in mathematics from Kyung Hee University, Seoul, Korea, in 1992 and 1994, respectively. He has been working toward the Ph.D. degree in the Department of Electrical and Computer Engineering, University of California, San Diego, La Jolla, since September 2003.

He worked at CAE, Semiconductor R&D Center, Samsung Electronics from 1994 to 2003. He has published over 20 papers and is the holder of five patents. His research interests include lithographic design for

yield and very large scale integration design-manufacturing interface. Mr. Park was the recipient of the 1998 Honorable Outstanding Researcher Award and the two Best Paper Awards from Samsung Electronics.